RL78/G15 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 500 of 765

Mar 7, 2023

12.7.4 Stop Condition Generation

After all data are transmitted to or received from the target slave, a stop condition is generated and the bus is released.

(1) Processing flow

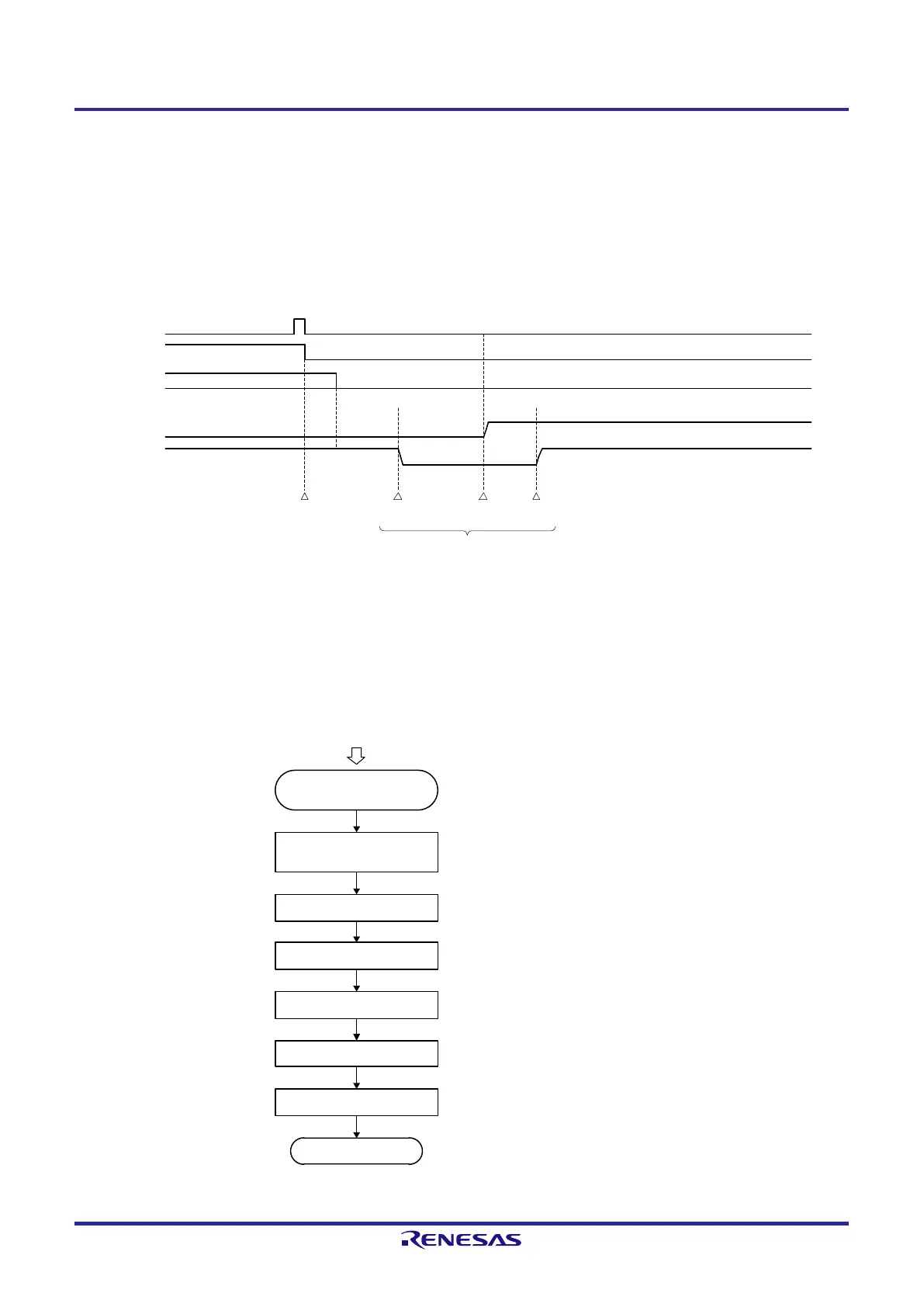

Figure 12-95. Timing Chart of Stop Condition Generation

SCLr output

STmn

SEmn

SOEmn

Note 1

SDAr output

SOmn bit

manipulation

Operation

stop

CKOmn bit

manipulation

Stop condition

Somn bit

manipulation

Note 1. During a receive operation, the SOEmn bit of serial output enable register m (SOEm) is cleared to 0 before

receiving the last data.

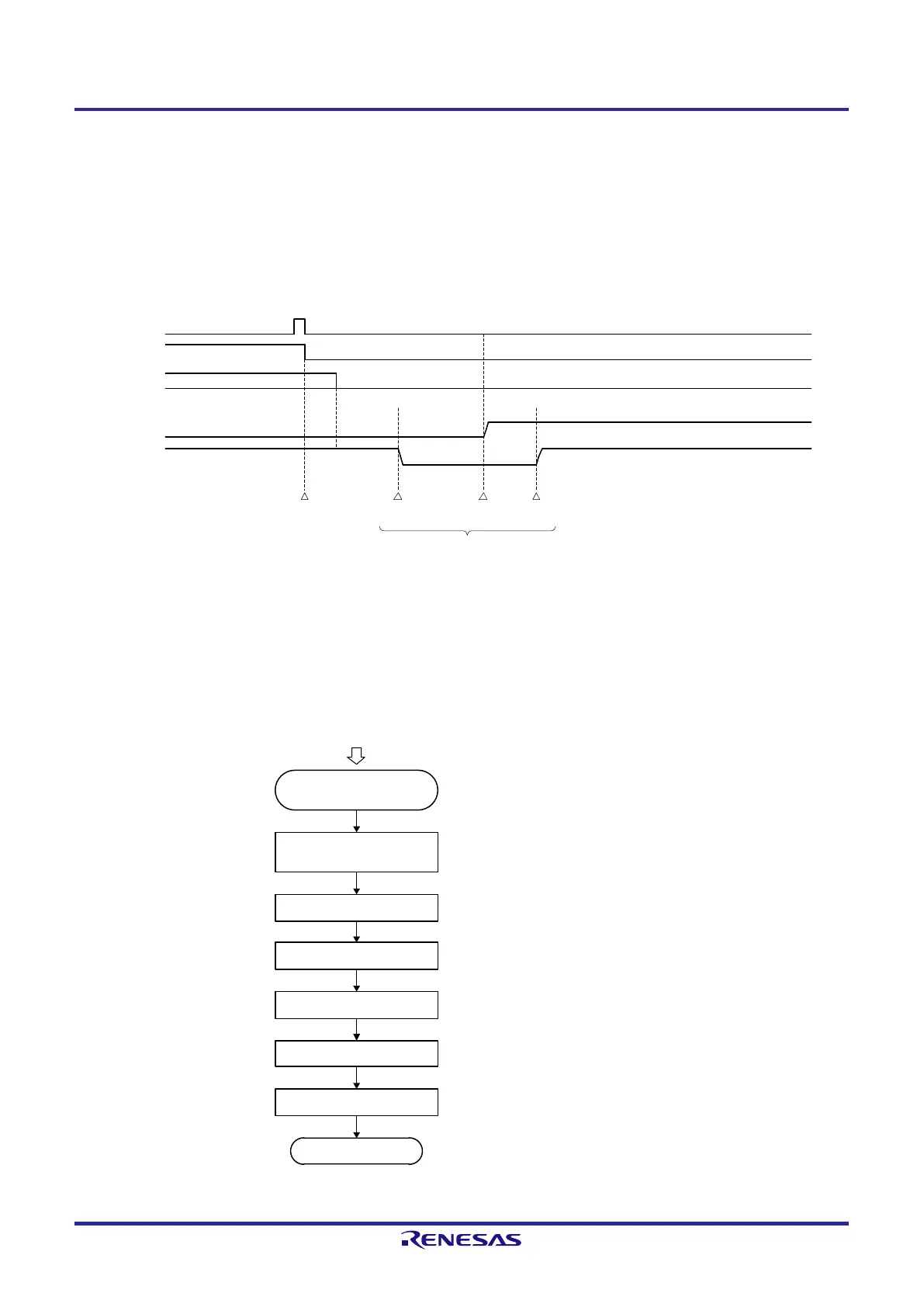

Figure 12-96. Flowchart of Stop Condition Generation

Writing 1 to the STmn bit

(the SEmn bit is cleared to 0)

Stops operation (CKOmn can be manipulated).

End of IIC communication

Completion of

data transmission/data reception

Writing 1 to the SOmn bit

Wait

Writing 1 to the CKOmn bit

Writing 0 to the SOmn bit

Writing 0 to the SOEmn bit

Starting generation of

stop condition

Disables output (SOmn can be manipulated).

Timing to satisfy the low width standard of SCL

for the I

2

C bus.

Secure a wait time so that the specifications of

the I

2

C bus on the slave side are satisfied.

Loading...

Loading...