RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 543 of 765

Mar 7, 2023

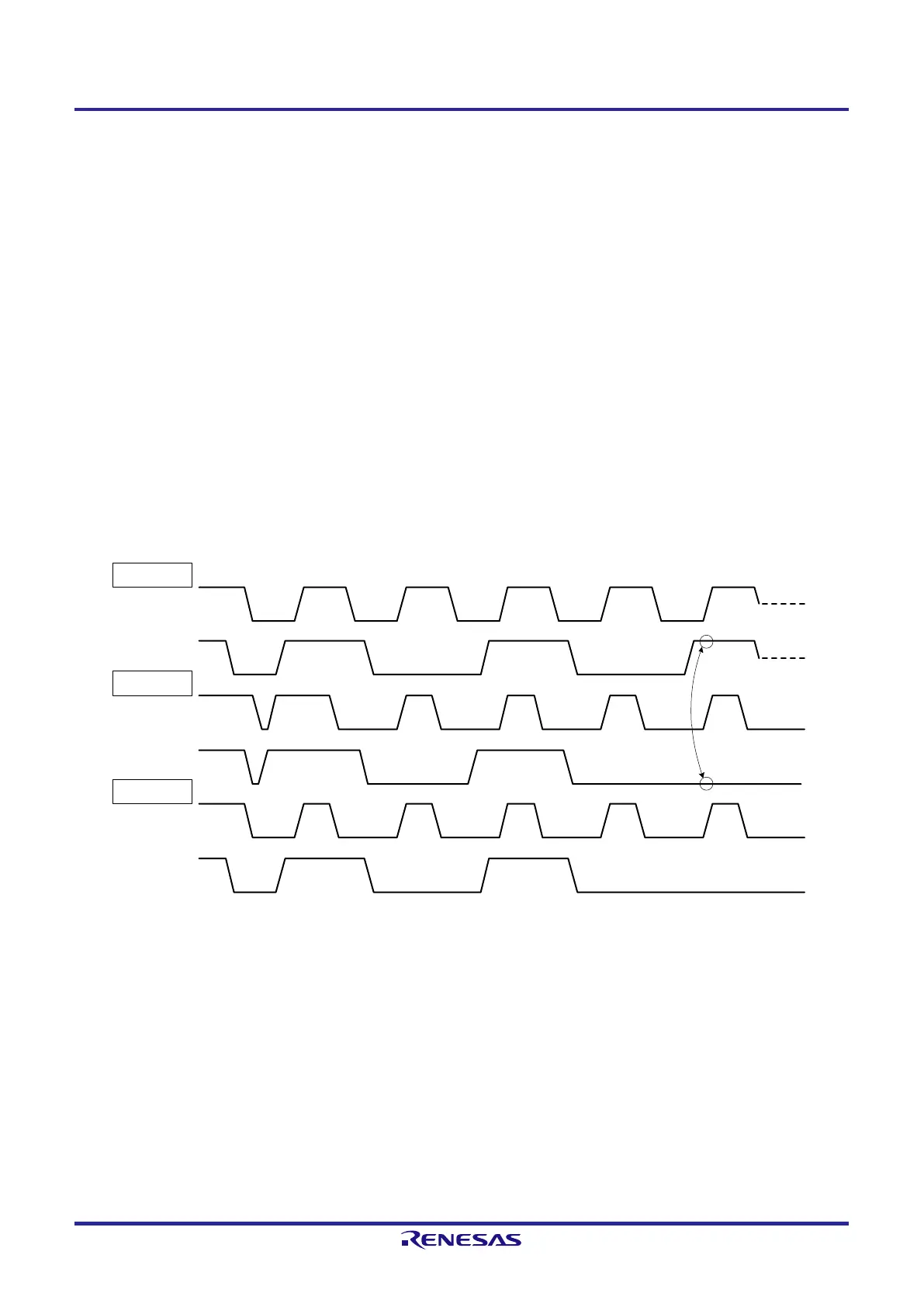

13.5.12 Arbitration

When several masters simultaneously generate a start condition (when the STT0 bit is set to 1 before the STD0 bit is set

to 1), master communication is performed while adjusting the clock cycles until the data differs. This kind of operation is

called arbitration.

A master which lost in arbitration sets the arbitration loss flag (ALD0) in the IICA status register 0 (IICS0) to 1 at the

timing it lost in arbitration and sets both the SCLA0 and SDAA0 lines to high impedance to release the bus.

A loss in arbitration is detected by checking ALD0 = 1 by software at the timing of the next interrupt request (the 8th or

9th clock cycle, when a stop condition is detected, etc.).

For details of interrupt request timing, see 13.5.8 Interrupt request (INTIICA0) generation timing and clock

stretching control.

Remark STD0: Bit 1 of IICA status register 0 (IICS0)

STT0: Bit 1 of IICA control register 00 (IICCTL00)

Figure 13-20. Arbitration Timing Example

SCLA0

SDAA0

SCLA0

SDAA0

SCLA0

SDAA0

Master 1

Master 2

Transfer line

Hi-Z

Hi-Z

Master 1 loses in arbitration

Loading...

Loading...