RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 533 of 765

Mar 7, 2023

13.5.2 Address

7-bit data that follows a start condition is defined as address.

An address is a 7-bit data segment that is output in order for the master to select a certain slave from among multiple

slaves connected to the bus line. Therefore, slaves on the bus line must have different addresses.

A slave detects this condition by the hardware and checks whether the 7-bit data matches the value of slave address

register 0 (SVA0). If the 7-bit data matches the value of the SVA0 register at this time, that slave is selected and it

communicates with the master until the master generates a start condition or stop condition.

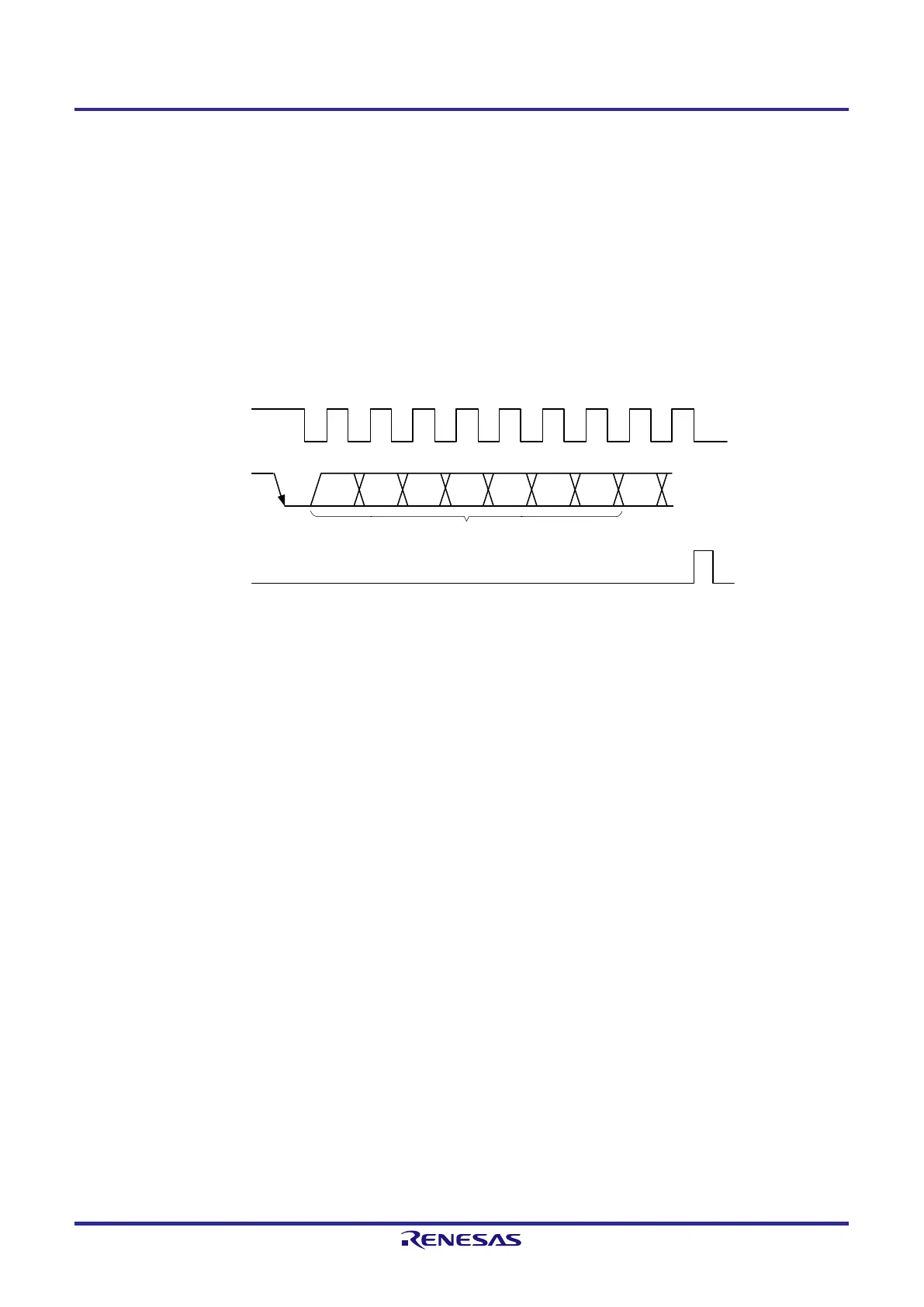

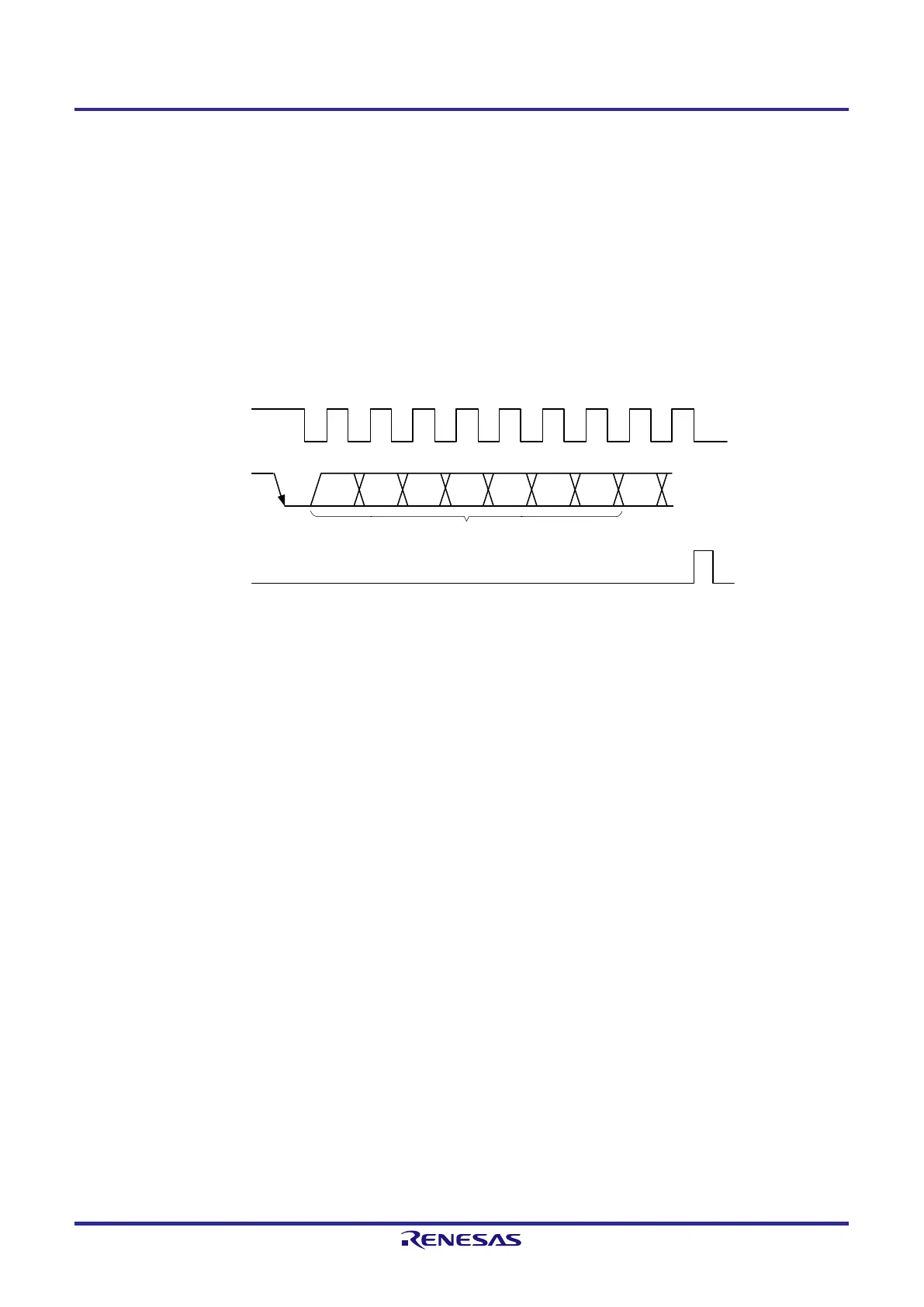

Figure 13-15. Address

SCLA0

SDAA0

INTIICA0

1 2 3 4 5 6 7 8 9

A6 A5 A4 A3 A2 A1 A0

__

R/W

Address

Note 1

Note 1. INTIICA0 is not generated if data other than the local address or extension code is received in slave

operation.

The address is output when 8 bits consisting of the slave address and the transfer direction described in 13.5.3 Transfer

direction specification are written to IICA shift register 0 (IICA0). The received address is written to the IICA0 register.

The slave address is assigned to the higher 7 bits of the IICA0 register.

Loading...

Loading...