RL78/G15 CHAPTER 7 12-BIT INTERVAL TIMER

R01UH0959EJ0110 Rev.1.10 Page 304 of 765

Mar 7, 2023

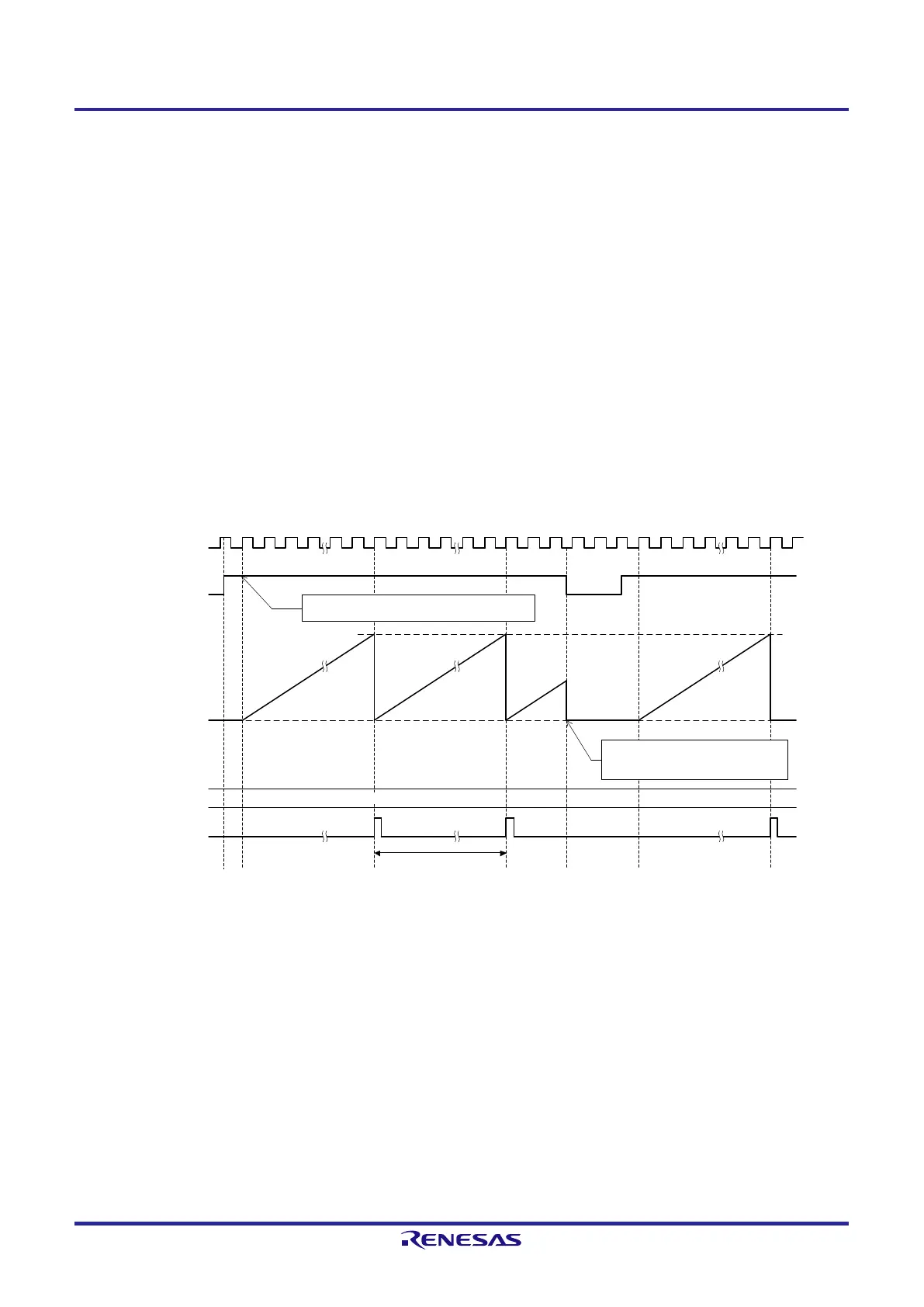

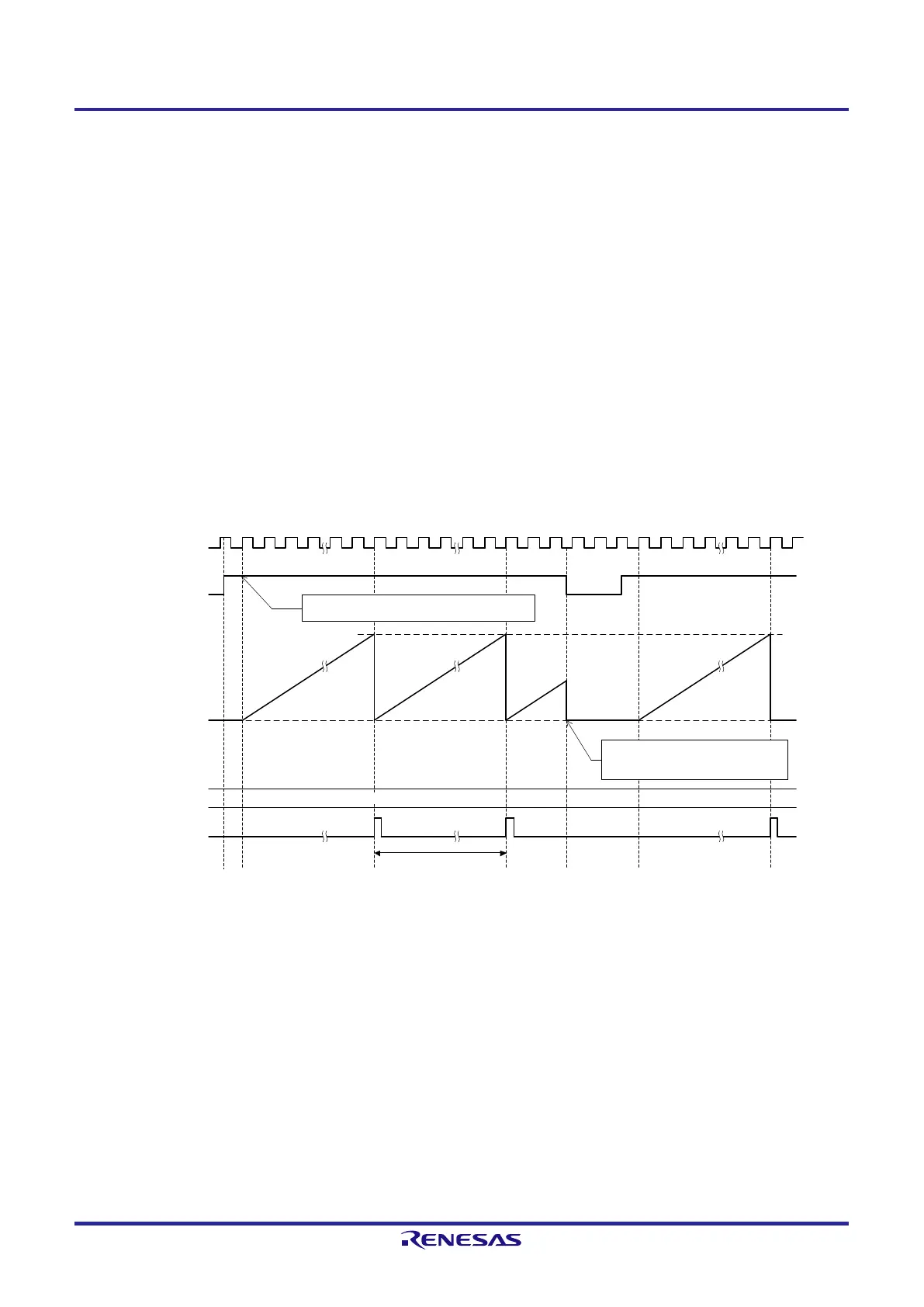

7.4 12-bit Interval Timer Operation

7.4.1 12-bit interval timer operation timing

The count value specified for the ITCMP11 to ITCMP0 bits is used as an interval to operate a 12-bit interval timer that

repeatedly generates interrupt requests (INTIT).

When the RINTE bit is set to 1, the 12-bit counter starts counting.

When the 12-bit counter value matches the value specified for the ITCMP11 to ITCMP0 bits, the 12-bit counter value is

cleared to 0, counting continues, and an interrupt request signal (INTIT) is generated at the same time.

The basic operation of the 12-bit interval timer is shown in Figure 7-5.

Figure 7-5. 12-bit Interval Timer Operation Timing

(ITCMP11 to ITCMP0 = 0FFH, count clock: f

IL

= 15 kHz)

0

FFH

0FFH

Counting starts at the rising edge of the first cycle of

the count clock signal after the RINTE bit is set to 1.

INTIT

ITCMP

11

to ITCMP0

12-bit counter

Count clock

RINTE

000H

Period (17.06 ms

)

The 12-bit counter is cleared

asynchronously with the count clock

signal when the RINTE bit is cleared to 0

.

Loading...

Loading...