RL78/G15 CHAPTER 11 COMPARATOR

R01UH0959EJ0110 Rev.1.10 Page 358 of 765

Mar 7, 2023

11.4.1 Comparator n Digital Filter Operation (n = 0, 1)

Comparator n incorporates a digital filter. The sampling clock is selected by the CnFCK1 and CnFCK0 bits in the

COMPFIR register. The comparator n output signal is sampled every sampling clock, and when the level of the output

signal matches three times, the digital filter output changes at the next sampling clock.

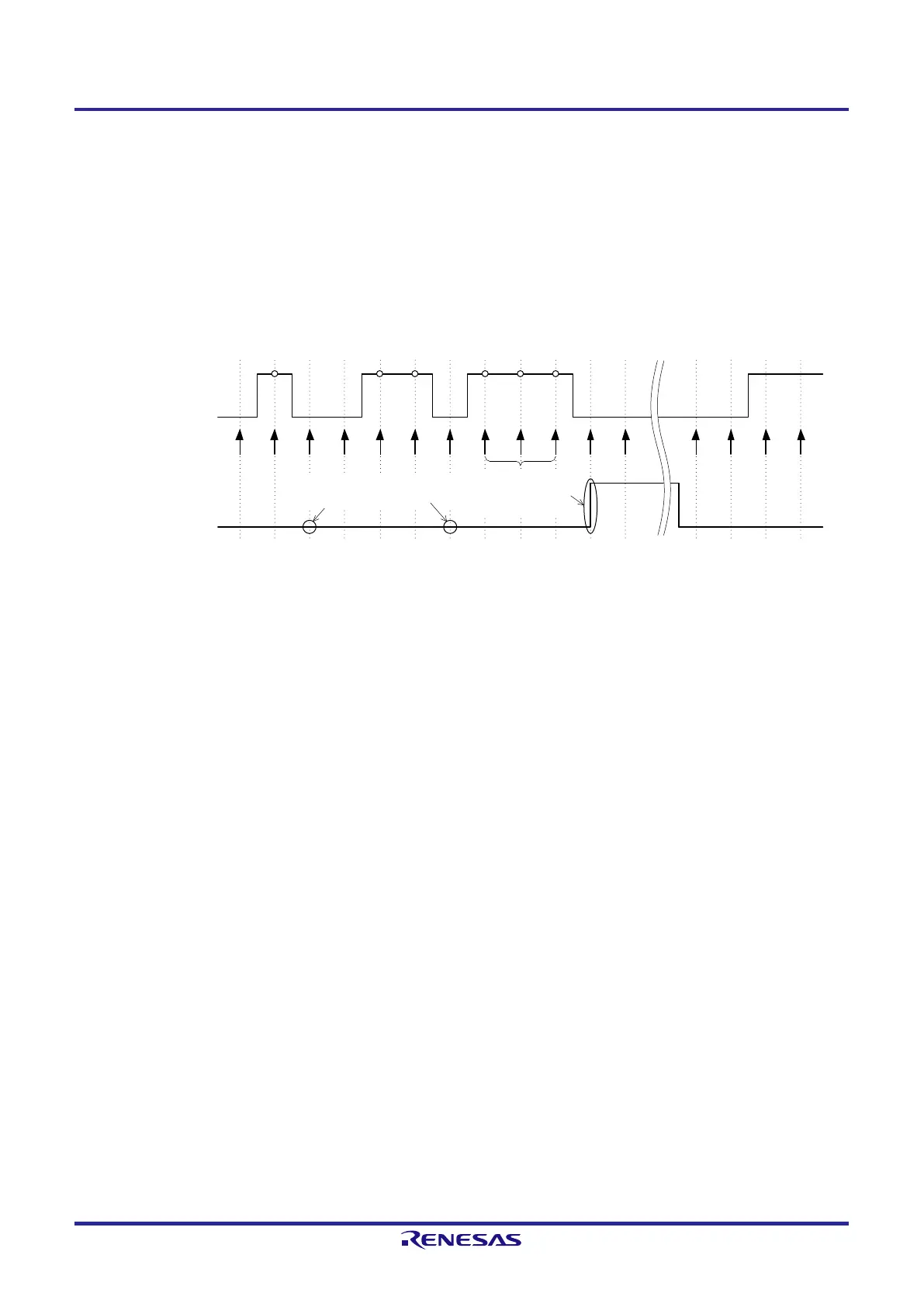

Figure 11-7 shows the comparator n (n = 0, 1) digital filter and interrupt operation example.

Figure 11-7. Comparator n (n = 0, 1) Digital Filter and Interrupt Operation Example

CnMON

Sampling timing

Comparator detection n

interrupt (INTCMPn

)

If the level does not match three times,

it is assumed to be noise and the

CMPIFn bit does not change.

Since the level matched

three times, it is recognized

as signal change and the

CMPIFn bit is set to 1.

Remark The operation example in Figure 11-7 applies when the digital filter is enabled (the CnFCK1 and CnFCK0

bits in the COMPFIR register = 01B, 10B, or 11B).

11.4.2 Comparator n Interrupt Operation (n = 0, 1)

When using the comparator n interrupt, set the CnIE bit in the COMPOCR register to 1 (interrupt request enabled). The

condition for interrupt request generation can be set by the COMPFIR register. The comparator outputs can also be

passed through the digital filter.

For details on the register settings, refer to 11.3.3 Comparator Filter Control Register (COMPFIR) and 11.3.4

Comparator Output Control Register (COMPOCR).

11.4.3 Comparator n Output (n = 0, 1)

The comparison result from the comparator can be output from the VCOUTn pin. The CnOP and CnOE bits in the

COMPOCR register are used to set the output polarity (inverted or non-inverted output) of the VCOUTn pin and enable

or disable the VCOUTn pin output, respectively. For details on the register settings, refer to 11.3.4 Comparator Output

Control Register (COMPOCR).

To output the comparator comparison result from the VCOUTn pin, follow the procedure shown in Figure 11-8

Procedure for Enabling Comparator Operation.

Loading...

Loading...