RL78/G15 CHAPTER 9 WATCHDOG TIMER

R01UH0959EJ0110 Rev.1.10 Page 313 of 765

Mar 7, 2023

9.3 Register Controlling Watchdog Timer

The watchdog timer is controlled by the watchdog timer enable register (WDTE).

9.3.1 Watchdog timer enable register (WDTE)

Writing “ACH” to the WDTE register clears the watchdog timer counter and starts counting again.

This register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 1AH or 9AH

Note 1

.

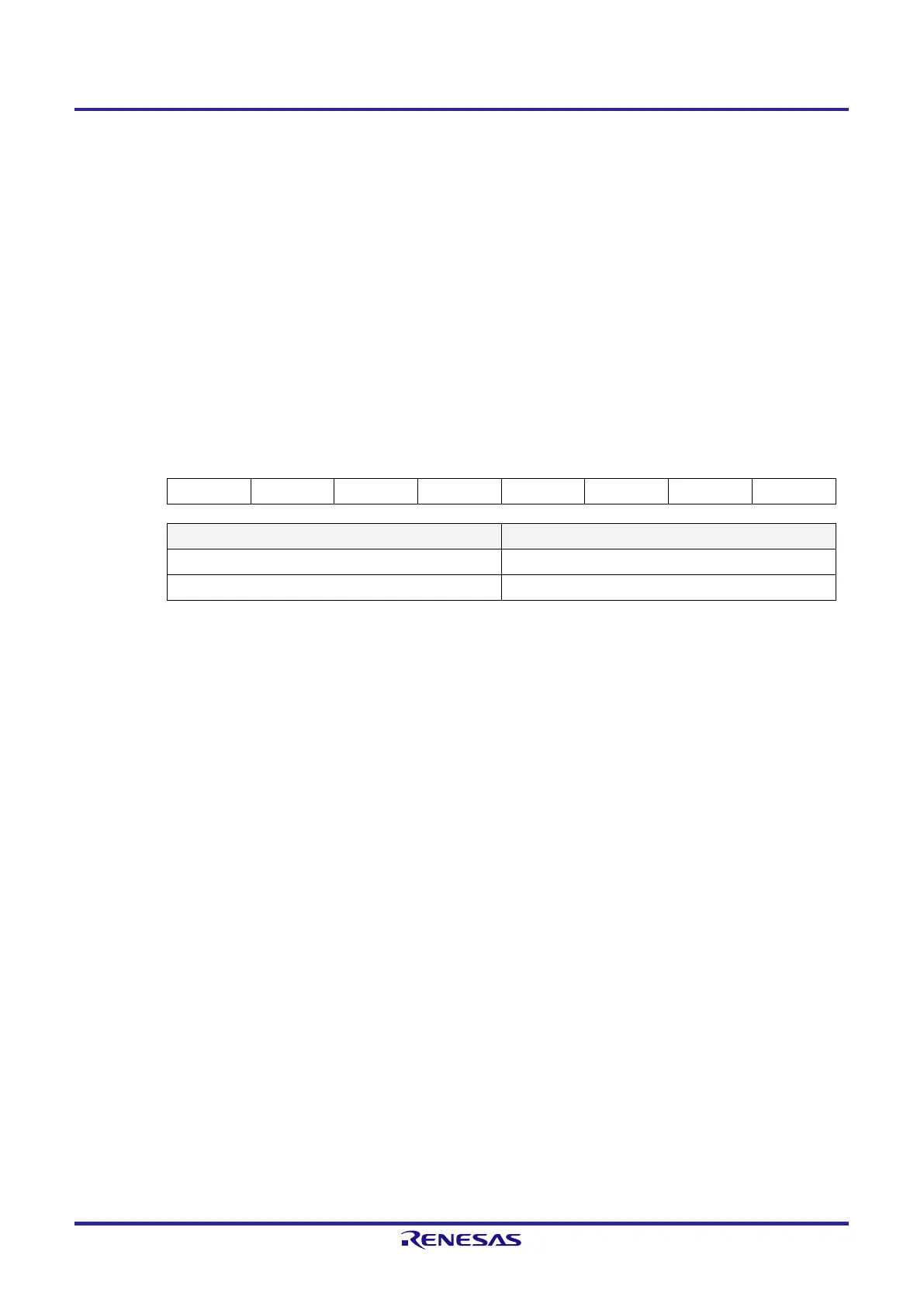

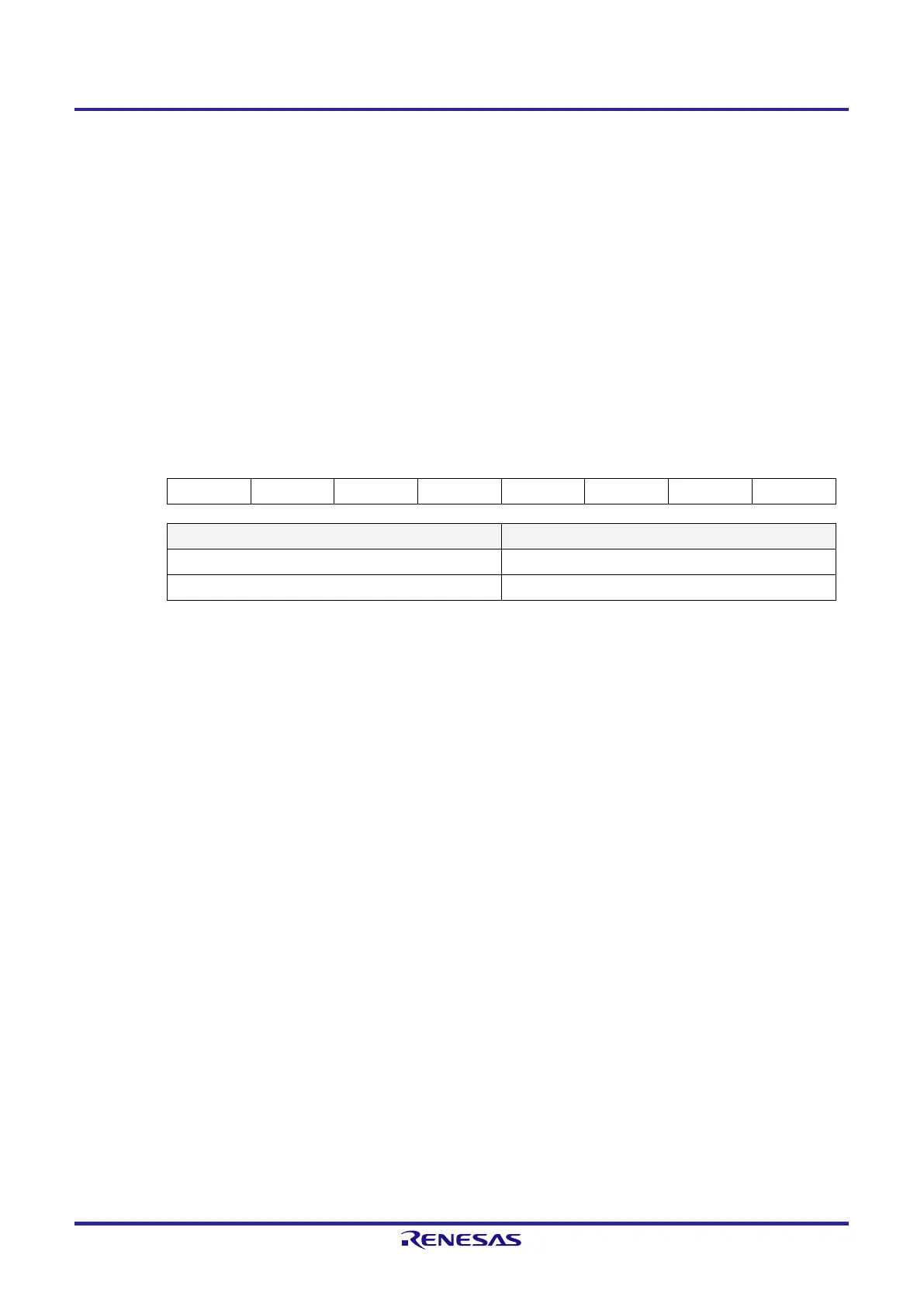

Figure 9-2. Format of Watchdog Timer Enable Register (WDTE)

Address: FFFABH After reset: 1AH/9AH

Note 1

R/W

Symbol 7 6 5 4 3 2 1 0

WDTE

WDTON Bit Setting Value WDTE Register Reset Value

0 (watchdog timer count operation disabled) 1AH

1 (watchdog timer count operation enabled) 9AH

Note 1. The WDTE register reset value differs depending on the WDTON bit setting value of the option byte

(000C0H). To operate the watchdog timer, set the WDTON bit to 1.

Caution 1. If a value other than “ACH” is written to the WDTE register, an internal reset signal is generated.

Caution 2. If a 1-bit memory manipulation instruction is executed for the WDTE register, an internal reset

signal is generated.

Caution 3. The value read from the WDTE register is 1AH/9AH (this differs from the written value (ACH)).

Loading...

Loading...