RL78/G15 CHAPTER 6 TIMER ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 224 of 765

Mar 7, 2023

6.6.5 Timer interrupt and TOmn pin output at count operation start

In the interval timer mode or capture mode, the MDmn0 bit in timer mode register mn (TMRmn) sets whether or not to

generate a timer interrupt at count start.

When MDmn0 is set to 1, the count operation start timing can be known by the timer interrupt (INTTMmn) generation.

In the other operation modes, neither timer interrupt at count operation start nor TOmn output is controlled.

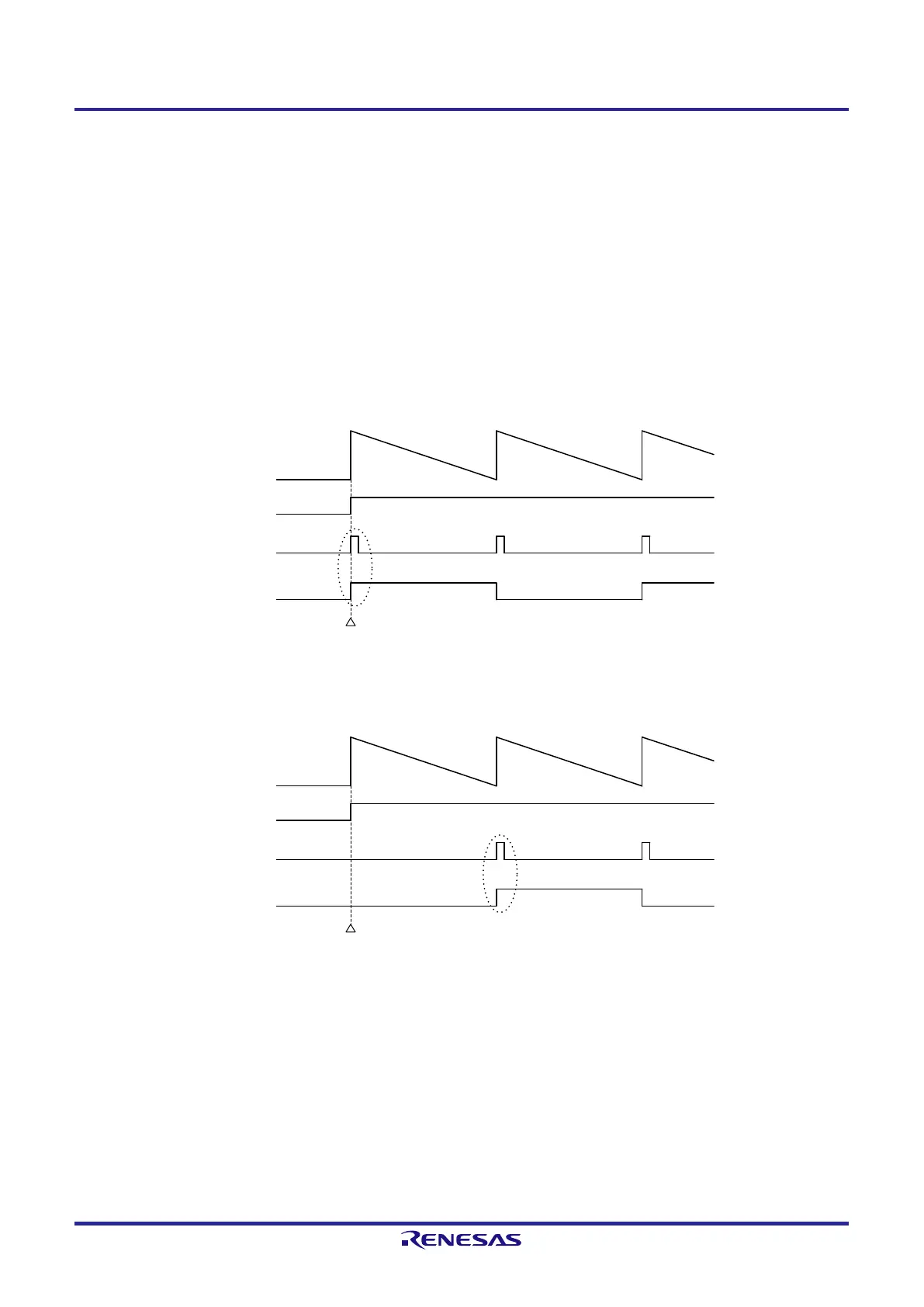

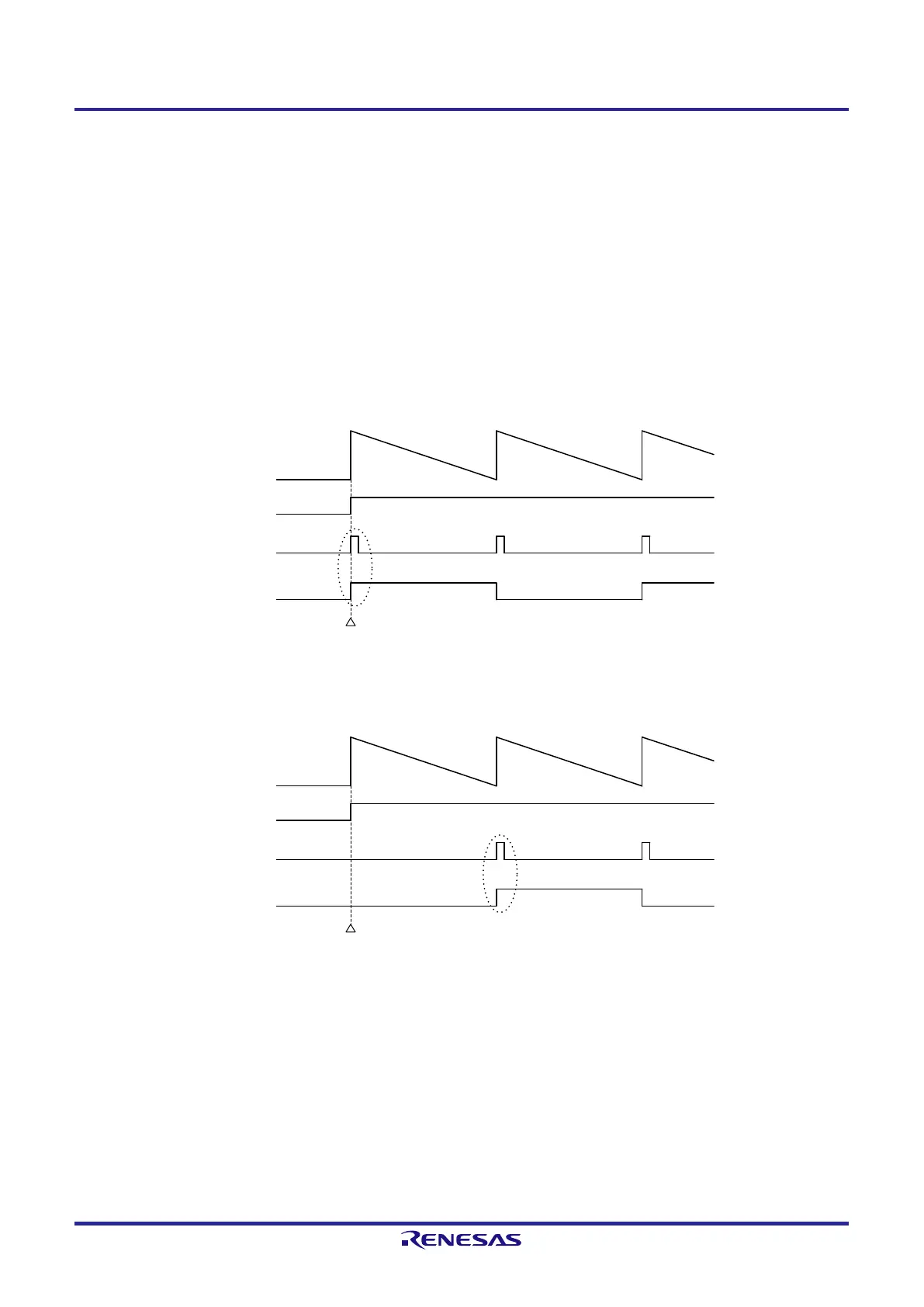

Figure 6-37 shows operation examples when the interval timer mode (TOEmn = 1, TOMmn = 0) is set.

Figure 6-37. Operation examples of timer interrupt at count operation start and TOmn output

(a) When MDmn0 is set to 1

TCRmn

TEmn

TOmn

INTTMmn

Count operation start

(b) When MDmn0 is set to 0

TCRmn

TEmn

TOmn

INTTMmn

Count operation start

When MDmn0 is set to 1, a timer interrupt (INTTMmn) is output at count operation start, and TOmn performs a toggle

operation.

When MDmn0 is set to 0, a timer interrupt (INTTMmn) is not output at count operation start, and TOmn does not change

either. After counting one cycle, INTTMmn is output and TOmn performs a toggle operation.

Remark m: Unit number (m = 0), n: Channel number (n = 0 to 7)

Loading...

Loading...