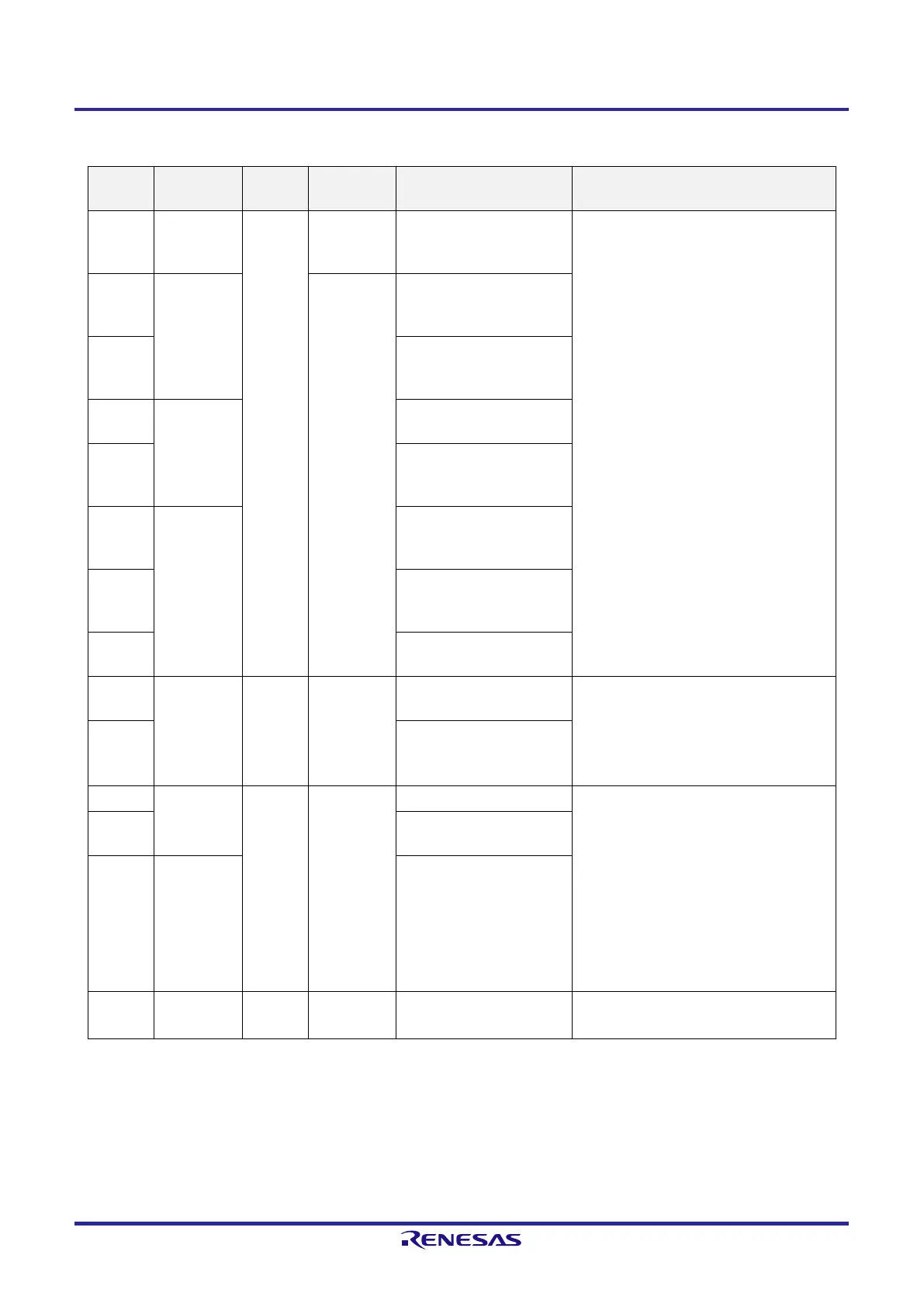

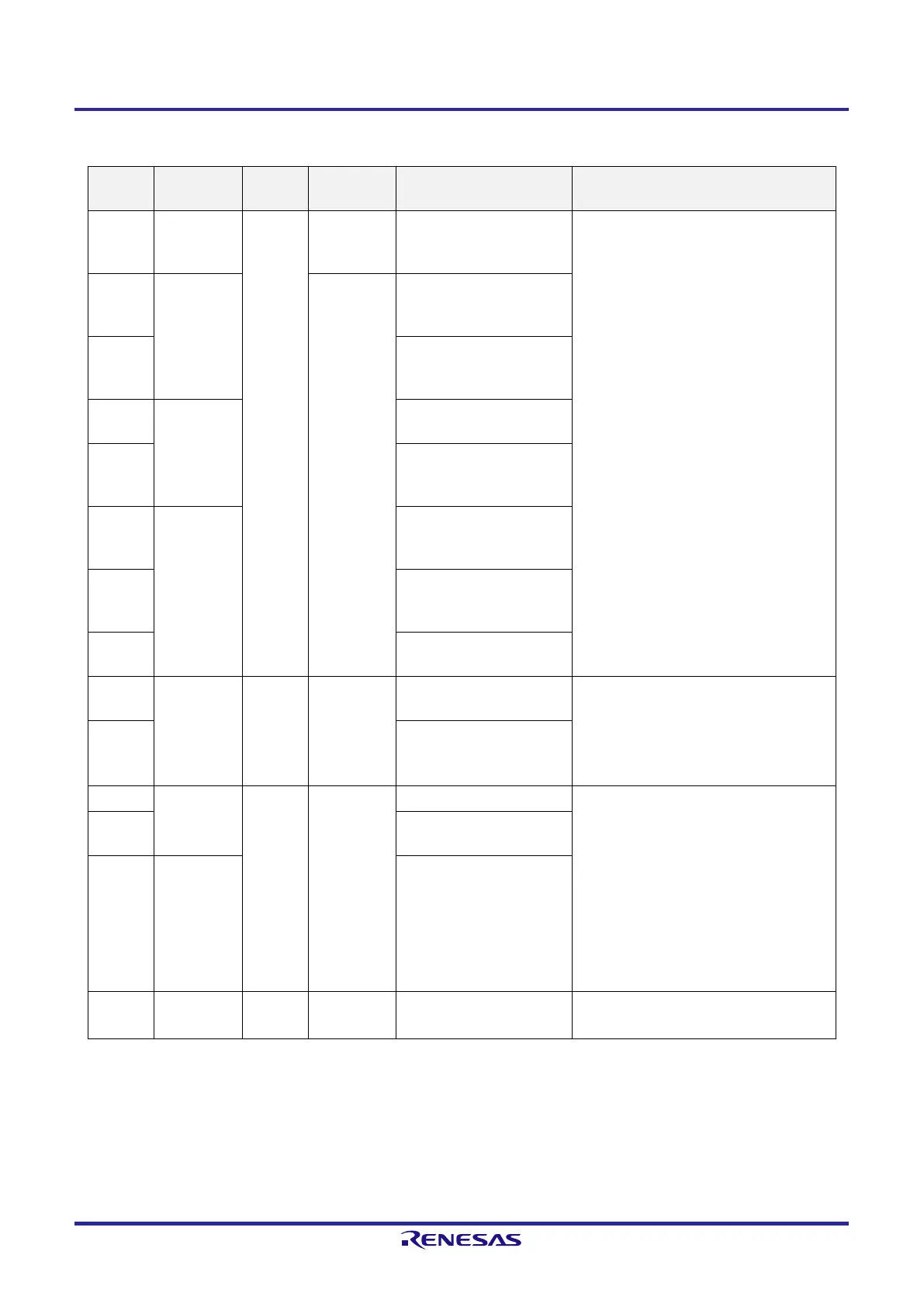

RL78/G15 CHAPTER 2 PIN FUNCTIONS

R01UH0959EJ0110 Rev.1.10 Page 40 of 765

Mar 7, 2023

2.1.3 16-pin products

Function

Name

Pin Type I/O

After Reset

Release

Alternate Function Function

P00 7-1-2 I/O Input port

TOOLTxD/INTP6/SO00/

TxD0/(SCK01/SCL01)/

(SCLA0)

Port 0.

8-bit I/O port.

Input/output can be specified in 1-bit units.

Use of an on-chip pull-up resistor can be

specified by a software setting at input port.

Output of P00, P01, and P03 to P07 can be

set to N-ch open-drain output (V

DD

tolerance).

P01 to P07 can be set to analog input

Note 1

.

P01 7-3-2 Analog input

TOOLRxD/ANI0/INTP5/SI00/

RxD0/SDA00/(TI02/TO02)/

(SI01)/(SDA01)/(SDAA0)

P02

PCLBUZ0/ANI1/VCOUT0/

INTP7/SCK00/SCL00/

(TI01/TO01)/(SO01)

P03 7-9-2

ANI2/IVCMP0/INTP4/TO00/

(TI00)/(SO00/TxD0)

P04

ANI3/IVREF0/INTP3/TI01/

TO01/(SI00/RxD0/SDA00)/

(SO00/TxD0)

P05 7-3-2

ANI4/TI02/TO02/SO01/

(INTP6)/(SCK00/SCL00)/

(SI00/RxD0/SDA00)

P06

ANI5/SI01/SDA01/SCLA0/

(PCLBUZ0)/(INTP7)/

(SCK00/SCL00)

P07

ANI6/SCK01/SCL01/SDAA0/

(INTP5)/(TO03)

P40 7-1-1 I/O Input port

TOOL0/INTP2/(PCLBUZ0)/

(TI01/TO01)

Port 4.

2-bit I/O port.

Input/output can be specified in 1-bit units.

Use of an on-chip pull-up resistor can be

specified by a software setting at input port.

P41

TI03/TO03/(INTP4)/

(TI02/TO02)

P121 7-2-2 I/O Input port X1/TI07/TO07/(INTP3) Port 12.

3-bit I/O port.

Use of an on-chip pull-up resistor can be

specified by a software setting at P121, P122,

and P125.

P125 is also used for the input pin for external

reset (RESET

¯¯¯¯¯¯

).

To use the pin for external reset, set the

PORTSELB bit in the option byte (000C1H) to

1.

P122

X2/EXCLK/TI05/TO05/

(INTP2)

P125 3-2-1 RESET

¯¯¯¯¯¯

/INTP1/(VCOUT0)

P137 2-1-2 Input Input port INTP0/TI00 Port 13.

1-bit input only port.

Note 1. Setting digital or analog to each pin can be done in the port mode control register 0 (PMC0) (can be set in 1-

bit units).

Remark Functions in parentheses can be assigned via settings in the peripheral I/O redirection registers 0 to 3

(PIOR0 to PIOR3). Refer to Figure 4-6 Format of Peripheral I/O Redirection Registers 0 to 3 (PIOR0 to

PIOR3).

Loading...

Loading...