RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 540 of 765

Mar 7, 2023

13.5.8 Interrupt request (INTIICA0) generation timing and clock stretching control

The setting of bit 3 (WTIM0) of IICA control register 00 (IICCTL00) generates INTIICA0 and controls clock stretching at

the timing shown in Table 13-2.

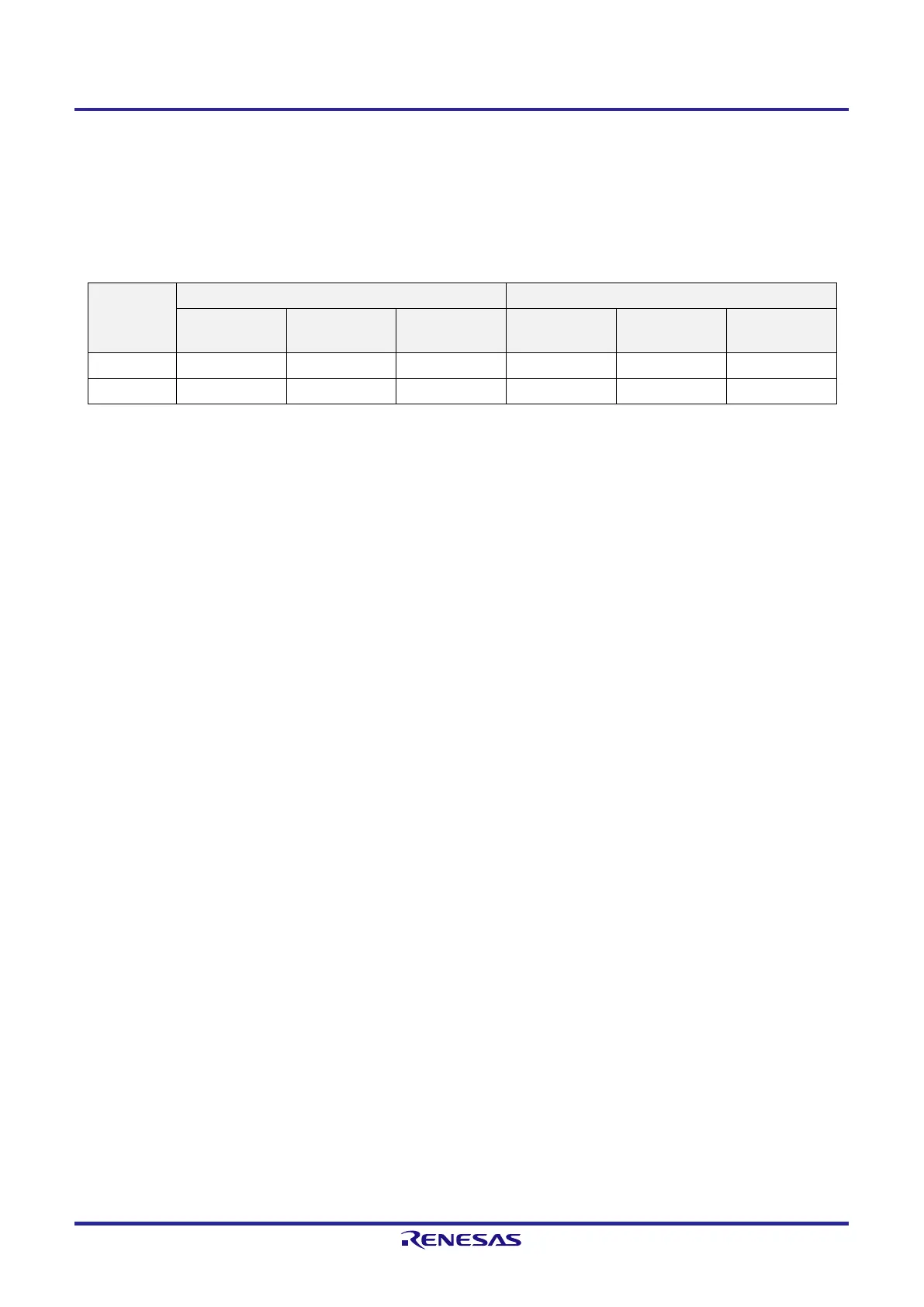

Table 13-2. INTIICA0 Generation Timing and Clock Stretching Control

WTIM0 In Slave Operation In Master Operation

Address Data Reception

Data

Transmission

Address Data Reception

Data

Transmission

0 9

Note 1, Note 2

8

Note 2

8

Note 2

9 8 8

1 9

Note 1, Note 2

9

Note 2

9

Note 2

9 9 9

Note 1. The slave’s INTIICA0 signal and clock stretching occur at the falling edge of the 9th clock only on matches

with the address set in slave address register 0 (SVA0).

At this point, ACK is generated regardless of the value set in bit 2 (ACKE0) of the IICCTL00 register. The

slave that has received an extension code generates INTIICA0 at the falling edge of the 8th clock.

However, if an address mismatch occurs after restart, INTIICA0 is generated at the falling edge of the 9th

clock, but clock stretching does not occur.

Note 2. If the received address does not match the setting of slave address register 0 (SVA0) and the extension code

is not received, neither INTIICA0 nor clock stretching occurs.

Remark The numbers in the table indicate the numbers of clock cycles of the serial clock. Interrupt requests and

control of clock stretching are both synchronized with the falling edge of the serial clock.

(1) In address transmission/reception

●

Slave operation: The timing of the interrupt and clock stretching is determined by the conditions described in Note 1

and Note 2 above, regardless of the setting of the WTIM0 bit.

●

Master operation: The interrupt and clock stretching occur at the falling edge of the 9th clock, regardless of the

setting of the WTIM0 bit.

(2) In data reception

●

Master/slave operation: The timing of the interrupt and clock stretching is determined by the setting of the WTIM0

bit.

(3) In data transmission

●

Master/slave operation: The timing of the interrupt and clock stretching is determined by the setting of the WTIM0

bit.

Loading...

Loading...