RL78/G15 APPENDIX A REVISION HISTORY

R01UH0959EJ0110 Rev.1.10 Page 760 of 765

Mar 7, 2023

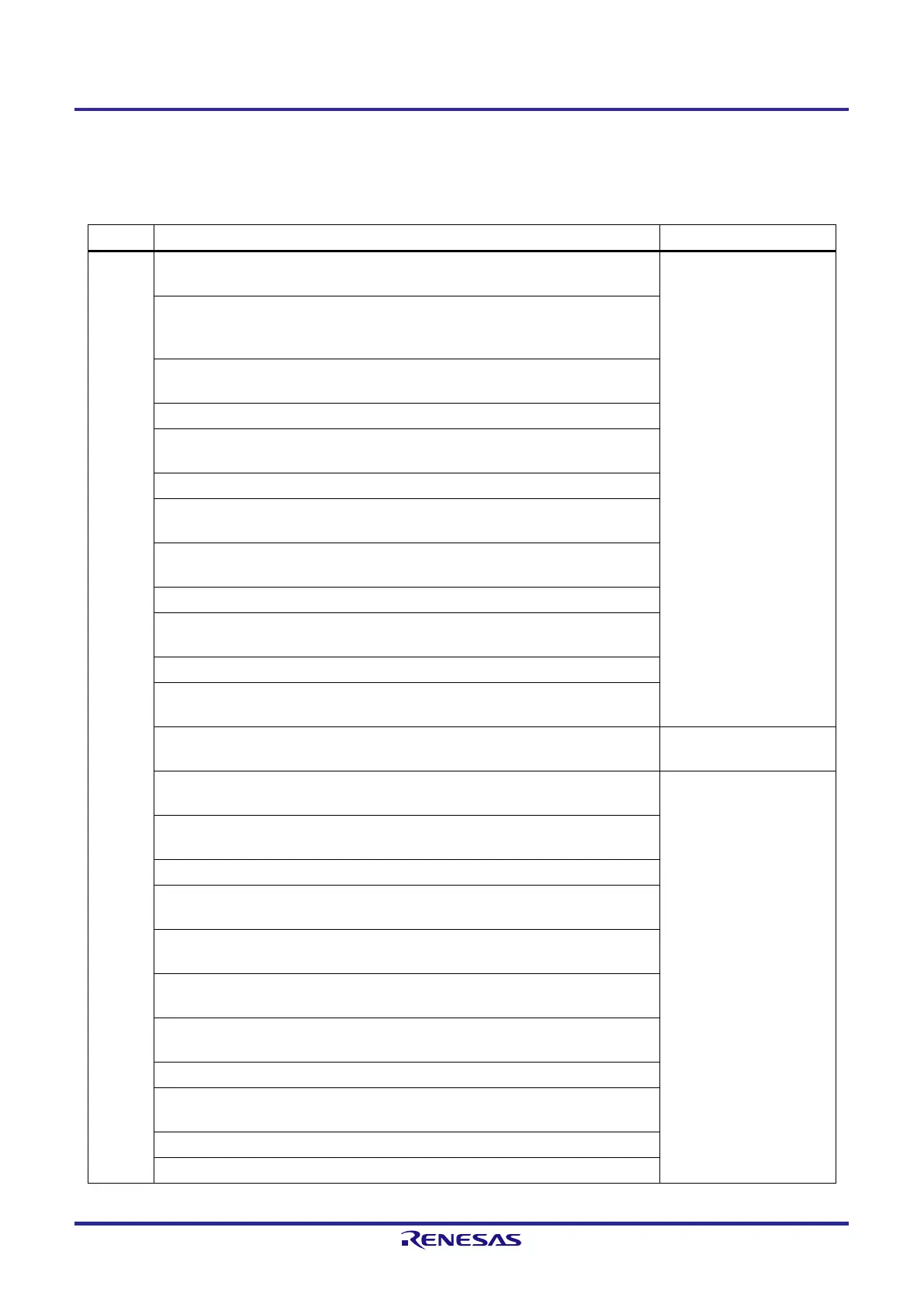

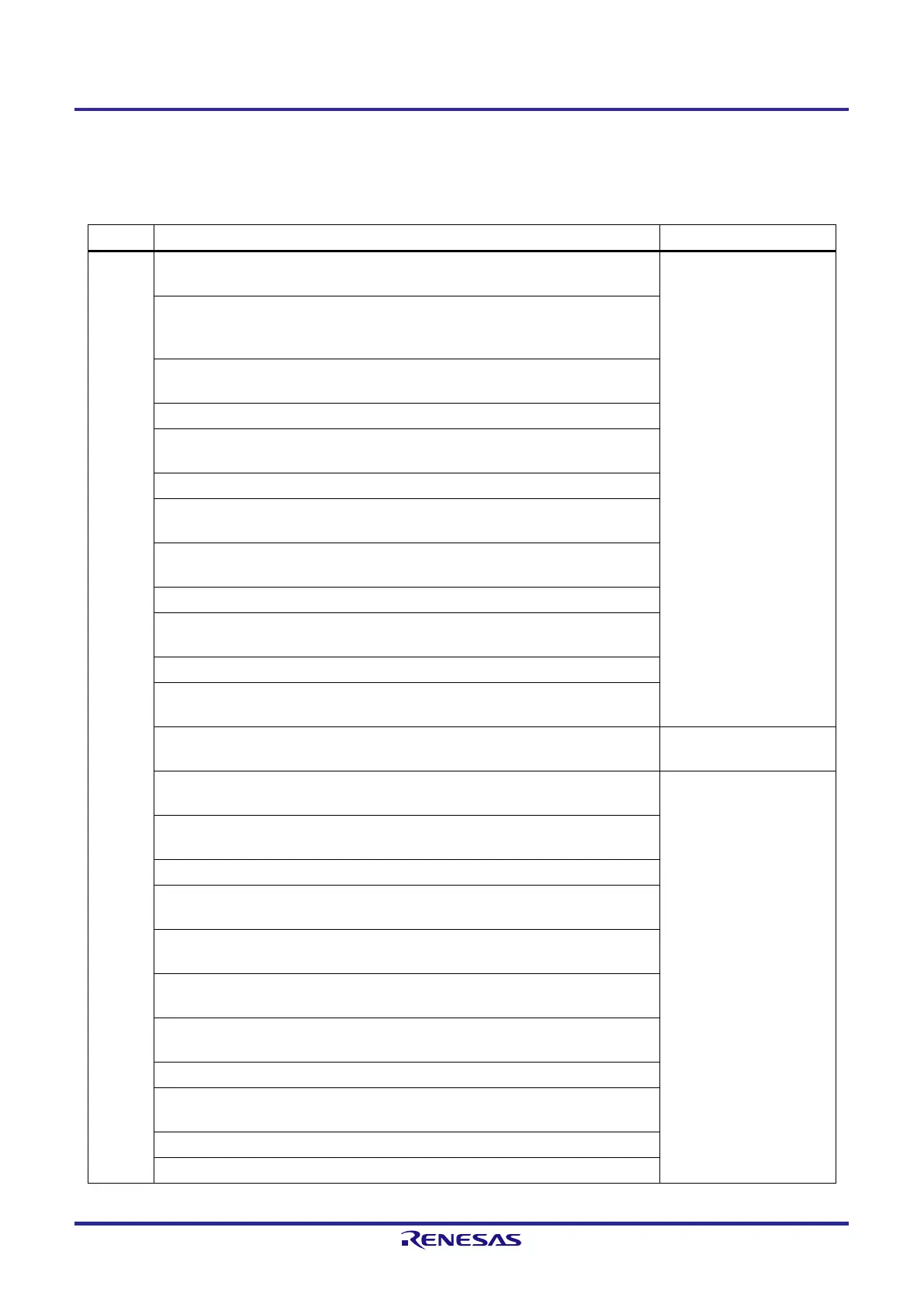

A.2 Revision History of Preceding Editions

Here is the revision history of the preceding editions. Chapter indicates the chapter of each edition.

(1/4)

Edition Description Chapter

Rev.1.00

Figure 1-1. Part Number, Memory Size, and Package of RL78/G15: Packaging

specifications, modified

CHAPTER 1 OUTLINE

Table 1-1. List of Ordering Part Numbers: The ordering part number was changed to list

the product name and the packaging specifications in respective columns. RENESAS

Code, added.

8-pin plastic WDFN (3 × 3 mm, 0.65-mm pitch): Pin name, modified for pin 2, 5. Pin

name order, changed for pin 1, 5 to 7.

Table 1-2. Multiplexed Functions of 8-pin Products, added

10-pin plastic LSSOP (4.4 × 3.6 mm, 0.65-mm pitch): Pin name, modified for pin 2, 7.

Pin name order, changed

Table 1-3. Multiplexed Functions of 10-pin Products, added

16-pin plastic SSOP (4.4 × 5.0 mm, 0.65-mm pitch): Pin name, modified for pin 3, 6. Pin

name order, changed for pin 2, 9 to 16.

16-pin plastic HWQFN (3 × 3 mm, 0.5-mm pitch): Pin name, modified for pin 1. Pin

name order, changed for pin 7 to 14, 16.

Table 1-4. Multiplexed Functions of 16-pin Products, added

20-pin plastic LSSOP (4.4 × 6.5 mm, 0.65-mm pitch): Pin name, modified for pin 5. Pin

name order, changed for pin 3, 4, 11 to 20.

Table 1-5. Multiplexed Functions of 20-pin Products, added

1.6 Outline of Functions: High-speed system clock for 16-pin and 20-pin in the table,

modified

2.2.2 Pins for each product (pins other than port pins): VCOUT0 and VCOUT1 in the

table, modified

CHAPTER 2 PIN

FUNCTIONS

Figure 3-1. Memory Map (R5F120x8 (x = 0, 1, 4, 6)): Note 1, deleted (Numbering change:

Note 2. → Note 1.)

CHAPTER 3 CPU

ARCHITECTURE

Figure 3-2. Memory Map (R5F120x7 (x = 0, 1, 4, 6)): Note 1, deleted (Numbering change:

Note 2. → Note 1.)

Table 3-5. SFR List (1/2): R/W for the comparator filter control register, modified

Table 3-6. Extended SFR (2nd SFR) List (1/4): High-speed on-chip oscillator frequency

select register, added

Table 3-6. Extended SFR (2nd SFR) List (1/4): R/W for the flash sequencer status

register L, modified

Table 3-6. Extended SFR (2nd SFR) List (1/4): R/W for the flash sequence status register

H, modified

Table 3-6. Extended SFR (2nd SFR) List (2/4): 16-bit manipulable bit range, enabled for

the serial output level register 0

Table 3-6. Extended SFR (2nd SFR) List (4/4): Timer clock select register 1, deleted

Table 3-6. Extended SFR (2nd SFR) List (4/4): Flash memory CRC operation result

register, deleted

Table 3-6. Extended SFR (2nd SFR) List (4/4): Note 2, added

Figure 3-38. Illegal Memory Access Detection Space: Notes (Note 1, Note 2), deleted

Loading...

Loading...