RL78/G15 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 461 of 765

Mar 7, 2023

(1) Register setting

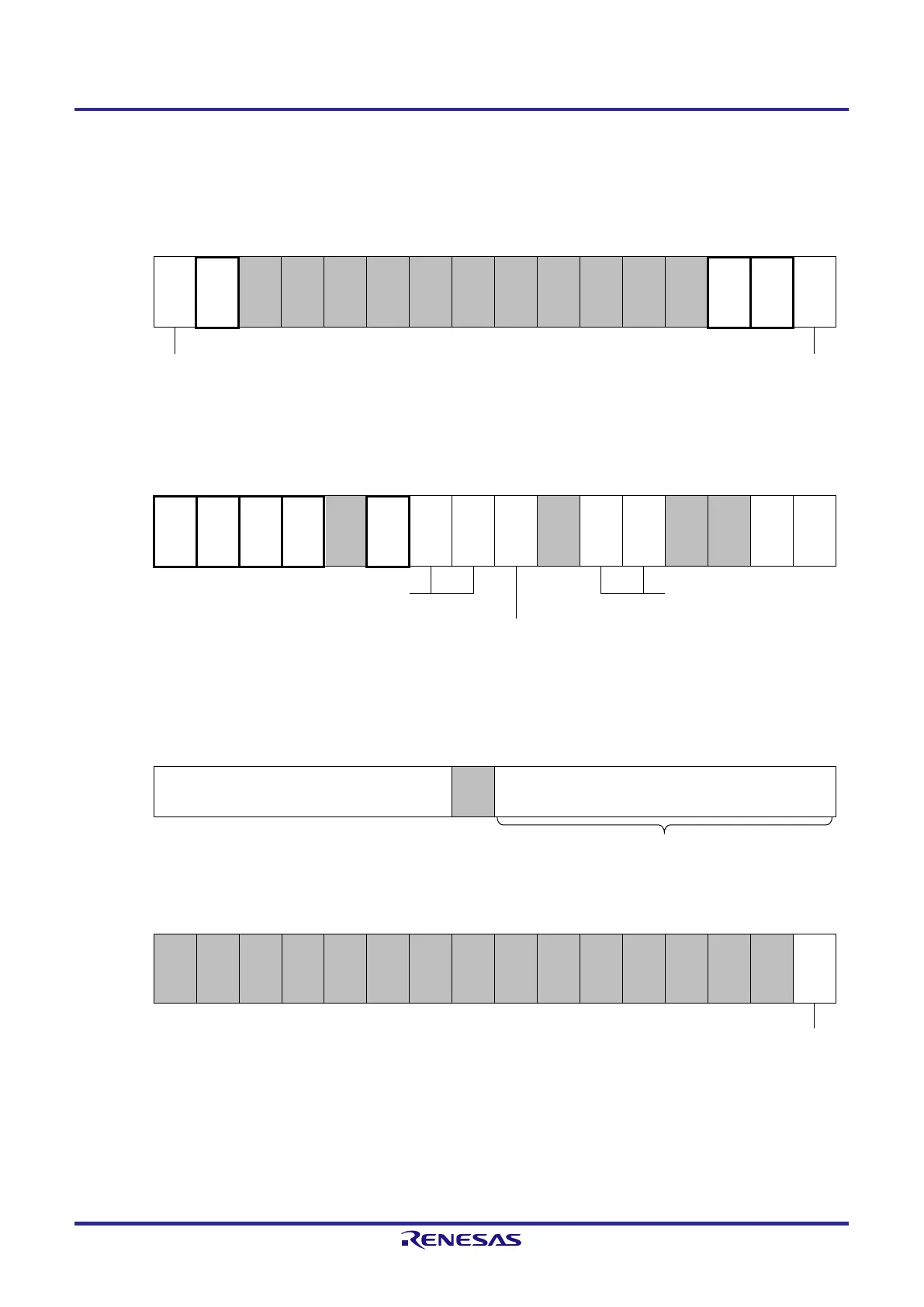

Figure 12-68. Example of Contents of Registers for UART Transmission of UART (UART0) (1/2)

(a) Serial mode register mn (SMRmn)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SMRmn

CKSm

n

CCSm

n

MDmn

2

MDmn

1

MDmn

0

0/1 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0/1

Operation clock (f

MCK

) of channel n

0: Prescaler output clock CKm0 set by the SPSm register

1: Prescaler output clock CKm1 set by the SPSm register

Interrupt source of channel n

0: Transfer end interrupt

1: Buffer empty interrupt

(b) Serial communication operation setting register mn (SCRmn)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SCRmn

TXEm

n

RXEm

n

DAPm

n

CKPm

n

EOCm

n

PTCm

n1

PTCm

n0

DIRmn

1

0

1

0

1 0 0 0 0 0 0/1 0/1 0/1 0 0/1 0/1 0 1 0/1 0/1

Setting of parity bit

00B: No parity

01B: Appending 0 parity

10B: Appending Even parity

11B: Appending Odd parity

Setting of stop bit

01B: Appending 1 bit

10B: Appending 2 bits

Selection of data transfer sequence

0: Outputs data with MSB first

1: Outputs data with LSB first

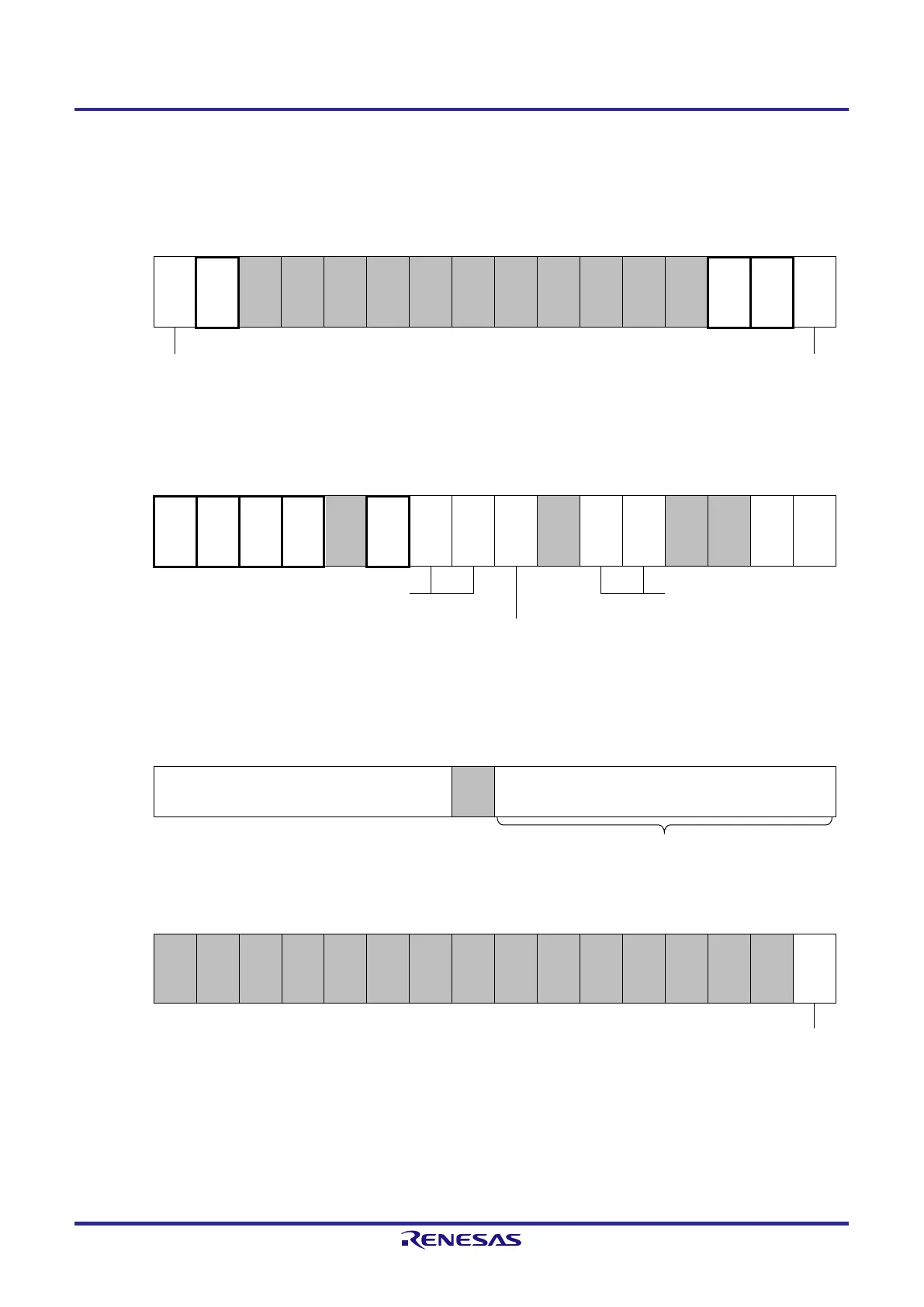

(c) Serial data register mn (SDRmn) (lower 8 bits: TXDq)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SDRmn Baud rate setting

Transmit data setting

0

Note 1

TXDq

(d) Serial output level register m (SOLm) … Set only the bit of the target channel.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOLm

SOLm

0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0/1

0: Non-reverse (normal) transmission

1: Reverse transmission

(Note 1, Note 2, and Remarks are listed on the next page.)

Loading...

Loading...