RL78/G15 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0959EJ0110 Rev.1.10 Page 478 of 765

Mar 7, 2023

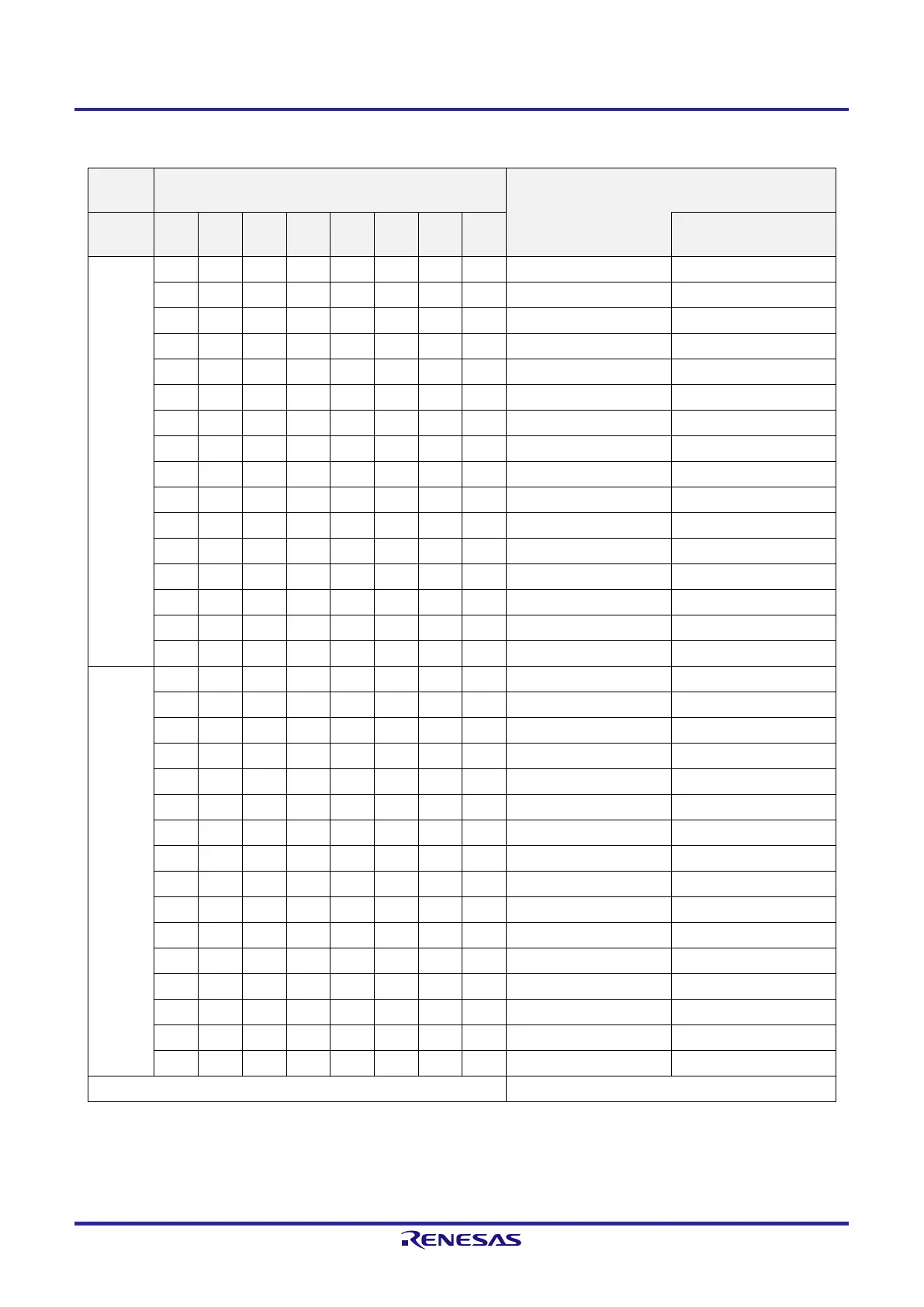

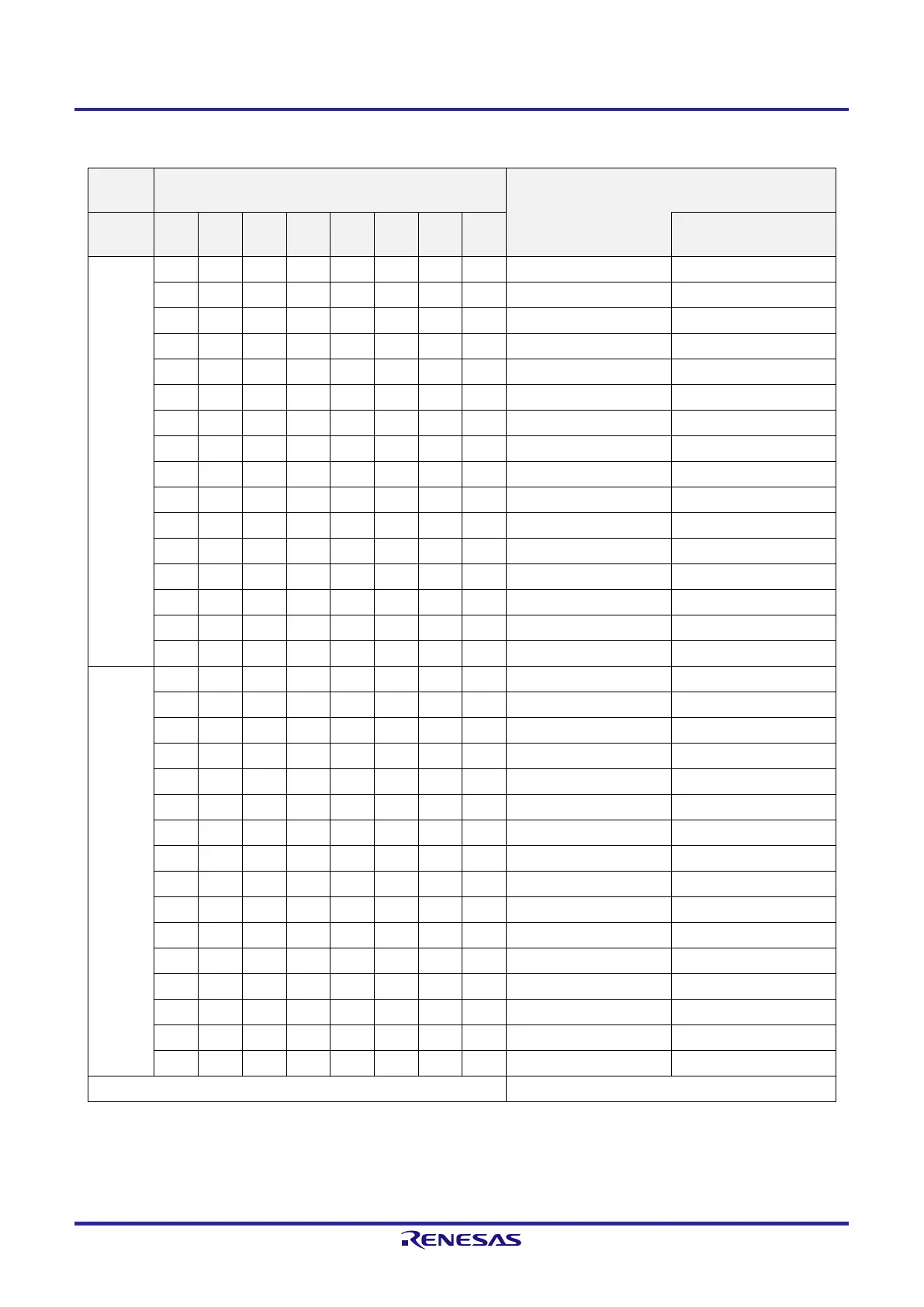

Table 12-3. Selection of Operation Clock For UART

SMRmn

Register

SPSm Register Operation Clock (f

MCK

)

Note 1

CKSmn

PRS

m13

PRS

m12

PRS

m11

PRS

m10

PRS

m03

PRS

m02

PRS

m01

PRS

m00

f

CLK

= 16 MHz

0 X X X X 0 0 0 0 f

CLK

16 MHz

X X X X 0 0 0 1 f

CLK

/2 8 MHz

X X X X 0 0 1 0 f

CLK

/2

2

4 MHz

X X X X 0 0 1 1 f

CLK

/2

3

2 MHz

X X X X 0 1 0 0 f

CLK

/2

4

1 MHz

X X X X 0 1 0 1 f

CLK

/2

5

500 kHz

X X X X 0 1 1 0 f

CLK

/2

6

250 kHz

X X X X 0 1 1 1 f

CLK

/2

7

125 kHz

X X X X 1 0 0 0 f

CLK

/2

8

62.5 kHz

X X X X 1 0 0 1 f

CLK

/2

9

31.25 kHz

X X X X 1 0 1 0 f

CLK

/2

10

15.63 kHz

X X X X 1 0 1 1 f

CLK

/2

11

7.81 kHz

X X X X 1 1 0 0 f

CLK

/2

12

3.91 kHz

X X X X 1 1 0 1 f

CLK

/2

13

1.95 kHz

X X X X 1 1 1 0 f

CLK

/2

14

977 Hz

X X X X 1 1 1 1 f

CLK

/2

15

488 Hz

1 0 0 0 0 X X X X f

CLK

16 MHz

0 0 0 1 X X X X f

CLK

/2 8 MHz

0 0 1 0 X X X X f

CLK

/2

2

4 MHz

0 0 1 1 X X X X f

CLK

/2

3

2 MHz

0 1 0 0 X X X X f

CLK

/2

4

1 MHz

0 1 0 1 X X X X f

CLK

/2

5

500 kHz

0 1 1 0 X X X X f

CLK

/2

6

250 kHz

0 1 1 1 X X X X f

CLK

/2

7

125 kHz

1 0 0 0 X X X X f

CLK

/2

8

62.5 kHz

1 0 0 1 X X X X f

CLK

/2

9

31.25 kHz

1 0 1 0 X X X X f

CLK

/2

10

15.63 kHz

1 0 1 1 X X X X f

CLK

/2

11

7.81 kHz

1 1 0 0 X X X X f

CLK

/2

12

3.91 kHz

1 1 0 1 X X X X f

CLK

/2

13

1.95 kHz

1 1 1 0 X X X X f

CLK

/2

14

977 Hz

1 1 1 1 X X X X f

CLK

/2

15

488 Hz

Other than above Setting prohibited

(Note 1 and Remarks are listed on the next page.)

Loading...

Loading...