RL78/G15 CHAPTER 13 SERIAL INTERFACE IICA

R01UH0959EJ0110 Rev.1.10 Page 535 of 765

Mar 7, 2023

When the master does not require the next data item during reception (TRC0 = 0), it must clear the ACKE0 bit to 0 so

that ACK is not generated. In this way, the master informs the slave (transmission side) of the end of data (transmission

will be stopped).

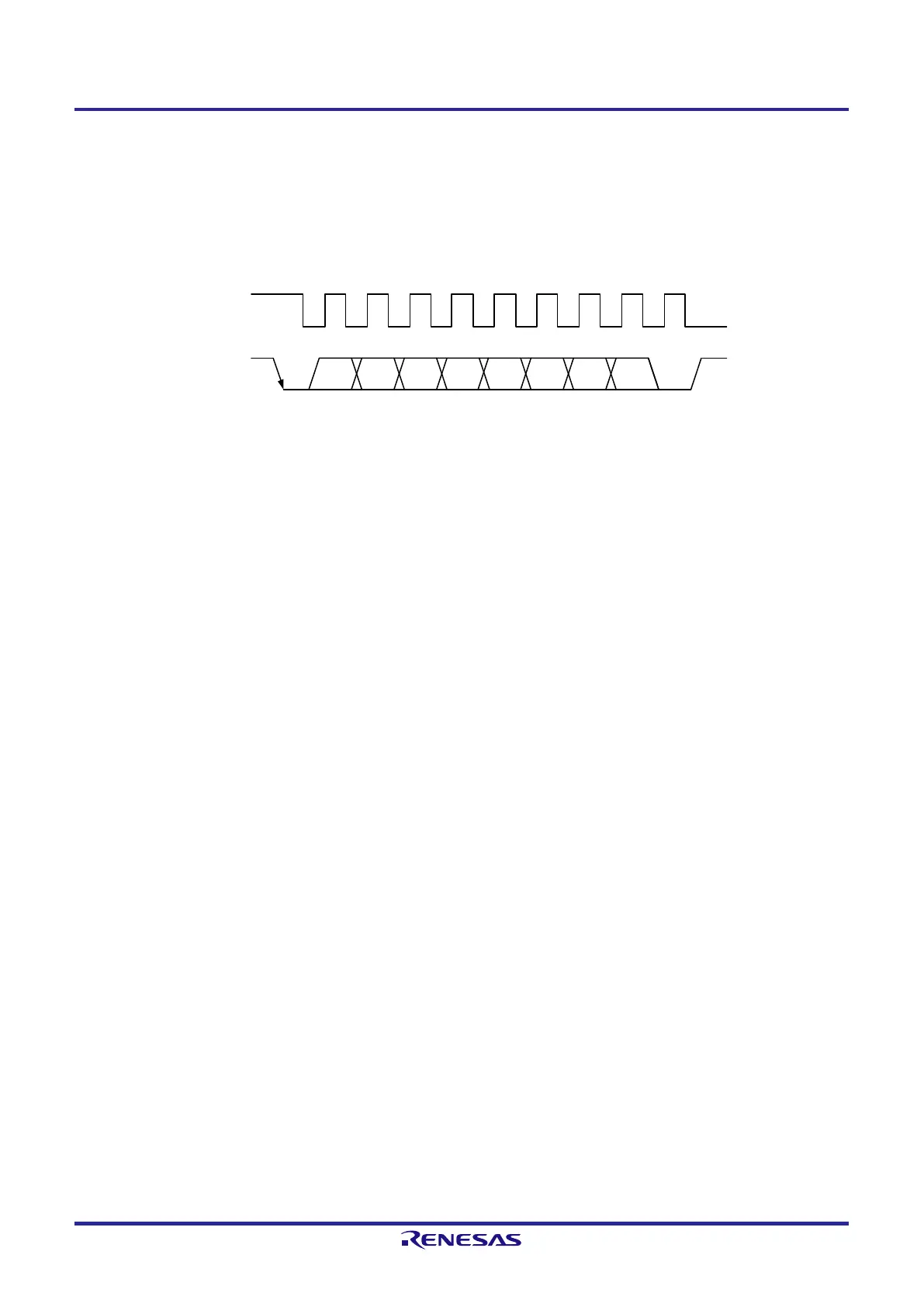

Figure 13-17. ACK

SCLA0

SDAA0

1 2 3 4 5 6 7 8 9

A6 A5 A4 A3 A2 A1 A0

__

R/W

ACK

When the local address is received, ACK is automatically generated, regardless of the value of the ACKE0 bit. When an

address other than the local address is received, ACK is not generated (NACK).

When an extension code is received, ACK is generated if the ACKE0 bit is set to 1 in advance.

How ACK is generated in data reception differs with the setting of the clock stretch timing as follows.

●

When the falling edge of the 8th clock is set (bit 3 (WTIM0) of the IICCTL00 register = 0):

By setting the ACKE0 bit to 1 before releasing clock stretching, ACK is generated at the falling edge of the 8th

clock of the SCLA0 pin.

●

When the falling edge of the 9th clock is set (bit 3 (WTIM0) of the IICCTL00 register = 1):

ACK is generated by setting the ACKE0 bit to 1 in advance.

Loading...

Loading...