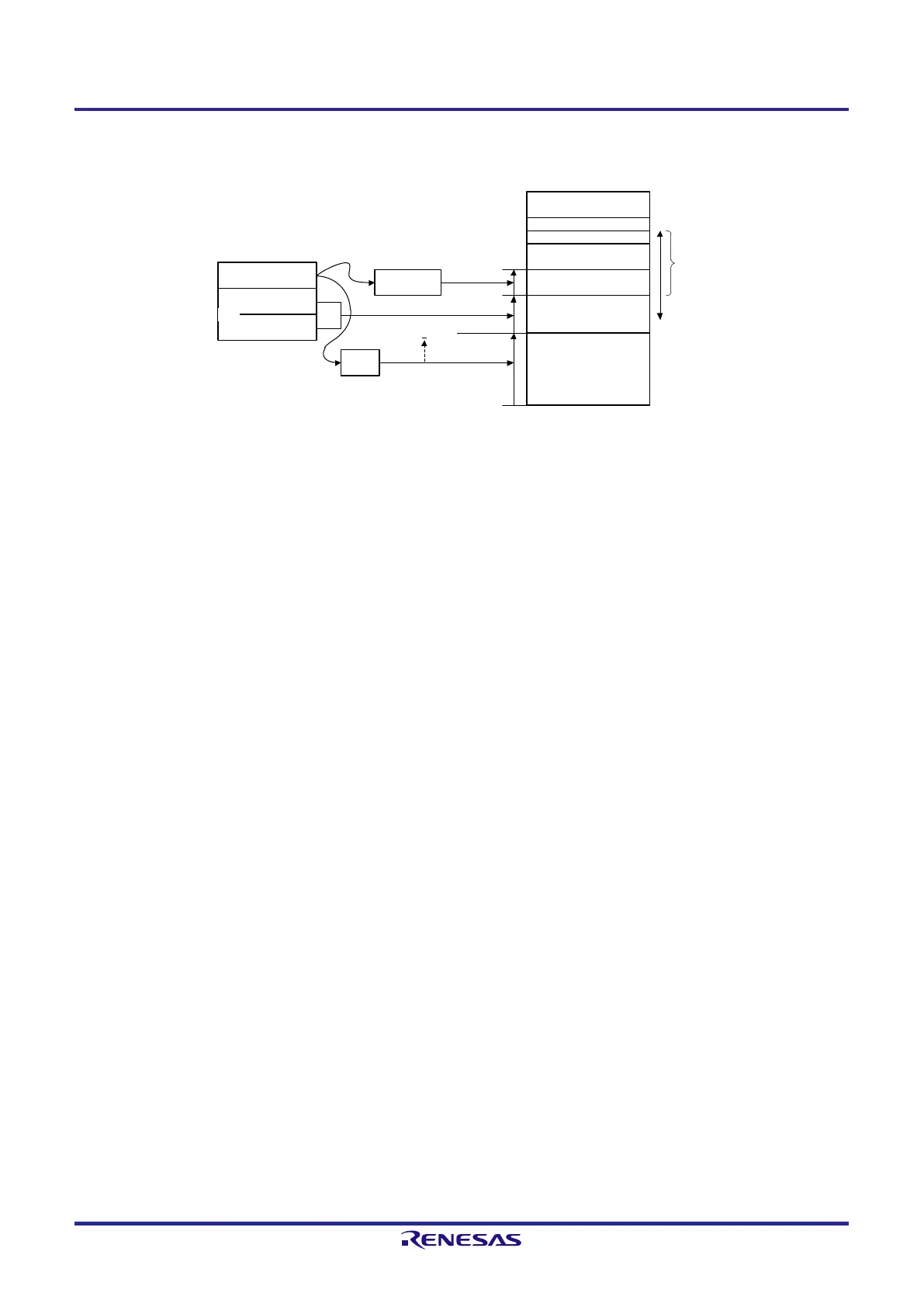

Instruction code

OP-code

Low Addr.

High Addr.

Target memory

XFFFFH

Memory

X0000H

<2>

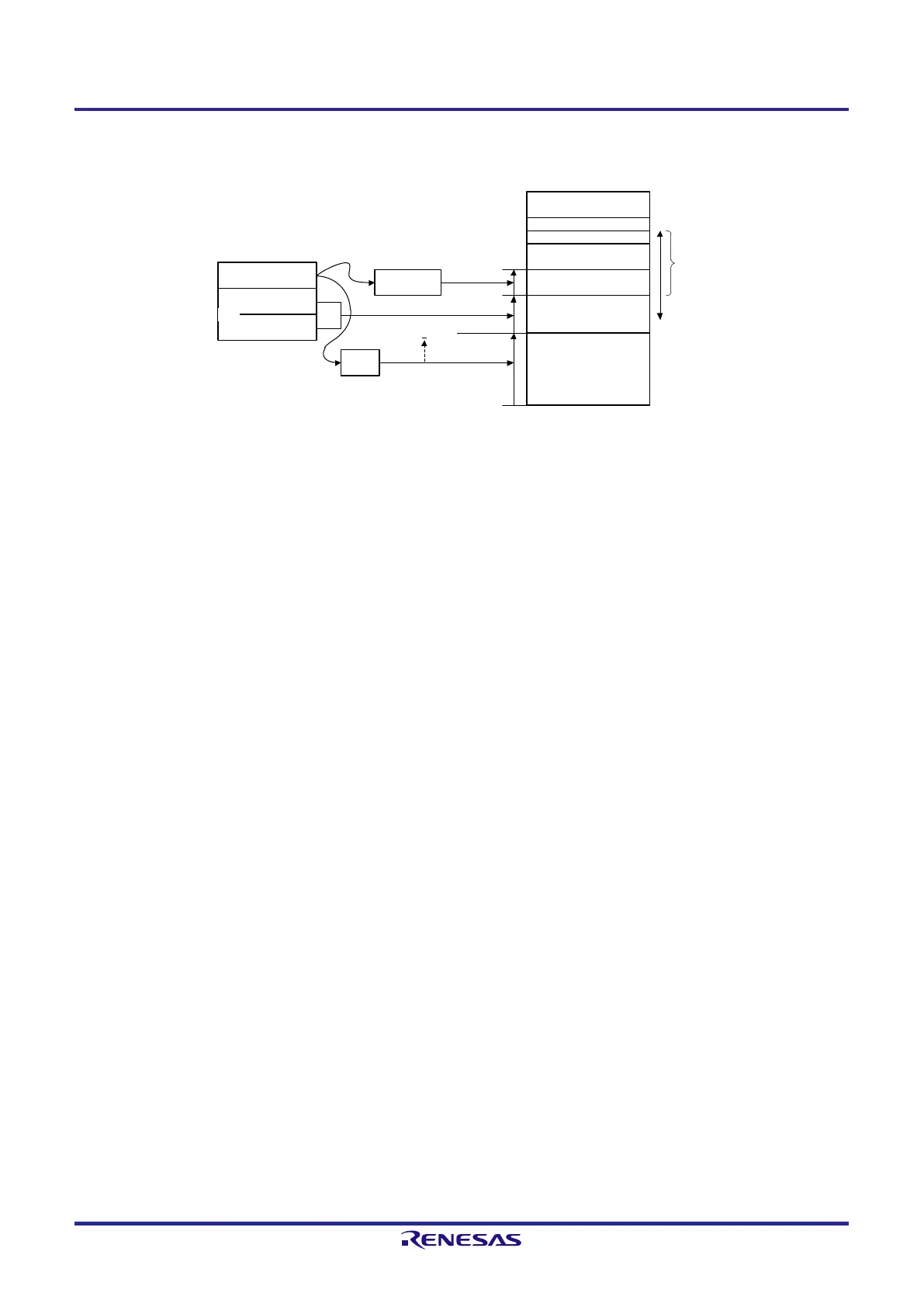

• The ES register <1> specifies a 64-Kbyte area within the overall

1-Mbyte space as the four higher-order bits, X, of the address

range.

• “word” <2> specifies the address where the target array of word-

sized data starts in the 64-Kbyte area specified in the ES register

<1>.

• A pair of registers <3> specifies an offset within the array to the

target location in memory.

ES: word [BC]

<1> <2> <3>

<2>

Address of a word

within an array

Array of

word-sized

data

ES

<1>

Specifies a

64-Kbyte area

X0000H

rp (BC)

<3>

Offset

<1>

<3>

Loading...

Loading...