R01UH0823EJ0100 Rev.1.00 Page 1178 of 1823

Jul 31, 2019

RX23W Group 35. I

2

C-bus Interface (RIICa)

35.10 Start Condition/Restart Condition/Stop Condition Issuing Function

35.10.1 Issuing a Start Condition

The RIIC issues a start condition when the ICCR2.ST bit is set to 1.

When the ST bit is set to 1, a start condition issuance request is made and the RIIC issues a start condition when the

ICCR2.BBSY flag is 0 (bus free state). When a start condition is issued normally, the RIIC automatically shifts to the

master transmit mode.

A start condition is issued in the following sequence.

Start condition issuance

(1) Drive the SDA0 line low (high level to low level).

(2) Ensure the time set in the ICBRH register and the start condition hold time.

(3) Drive the SCL0 line low (high level to low level).

(4) Detect low level of the SCL0 line and ensure the low-level period of SCL0 line set in the ICBRL register.

35.10.2 Issuing a Restart Condition

The RIIC issues a restart condition when the ICCR2.RS bit is set to 1.

When the RS bit is set to 1, a restart condition issuance request is made and the RIIC issues a restart condition when the

ICCR2.BBSY flag is 1 (bus busy state) and the ICCR2.MST bit is 1 (master mode).

A restart condition is issued in the following sequence.

Restart condition issuance

(1) Release the SDA0 line.

(2) Ensure the low-level period of SCL0 line set in the ICBRL register.

(3) Release the SCL0 line (low level to high level).

(4) Detect a high level of the SCL0 line and ensure the time set in the ICBRL register and the restart condition setup

time.

(5) Drive the SDA0 line low (high level to low level).

(6) Ensure the time set in the ICBRH register and the restart condition hold time.

(7) Drive the SCL0 line low (high level to low level).

(8) Detect a low level of the SCL0 line and ensure the low-level period of SCL0 line set in the ICBRL register.

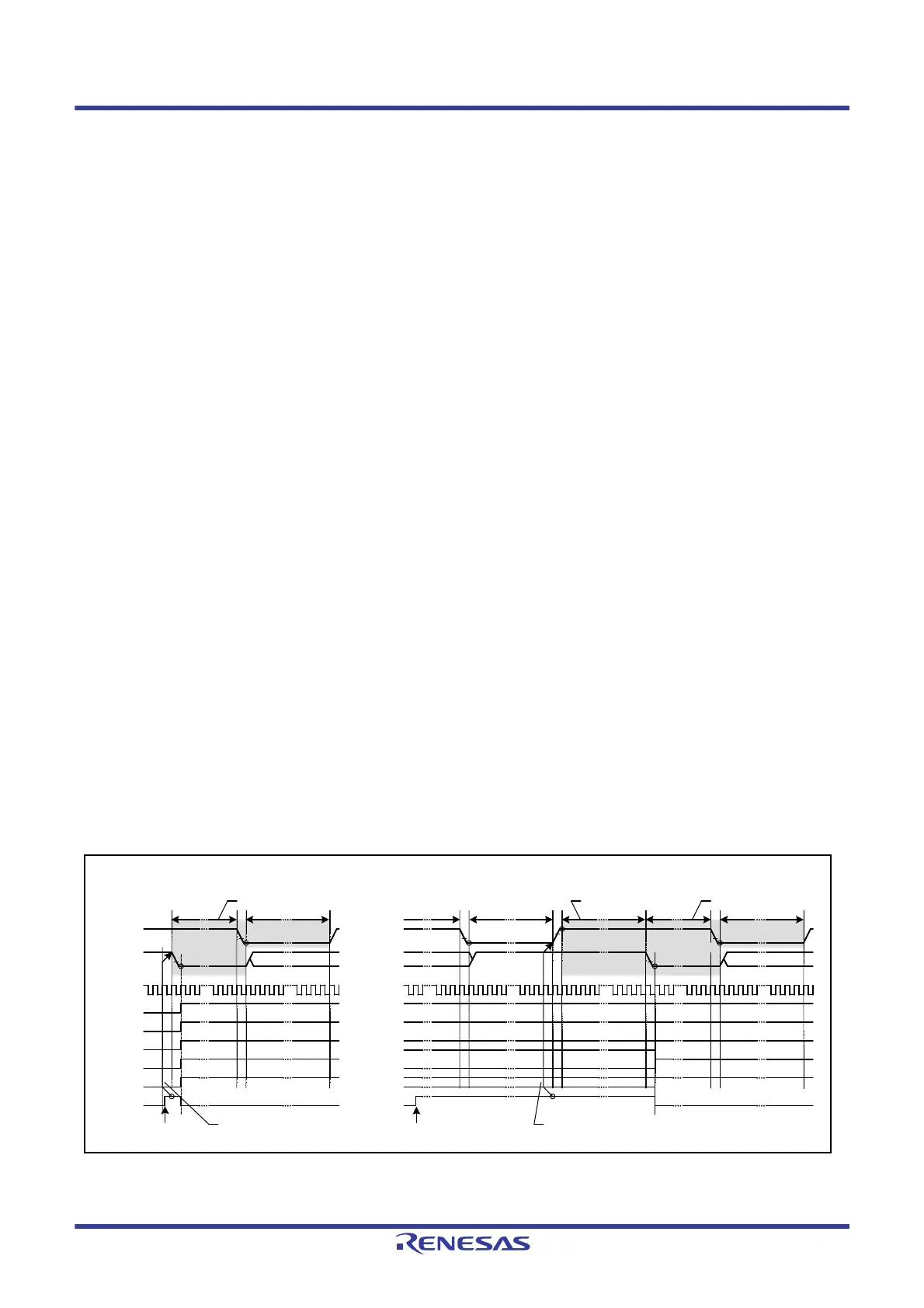

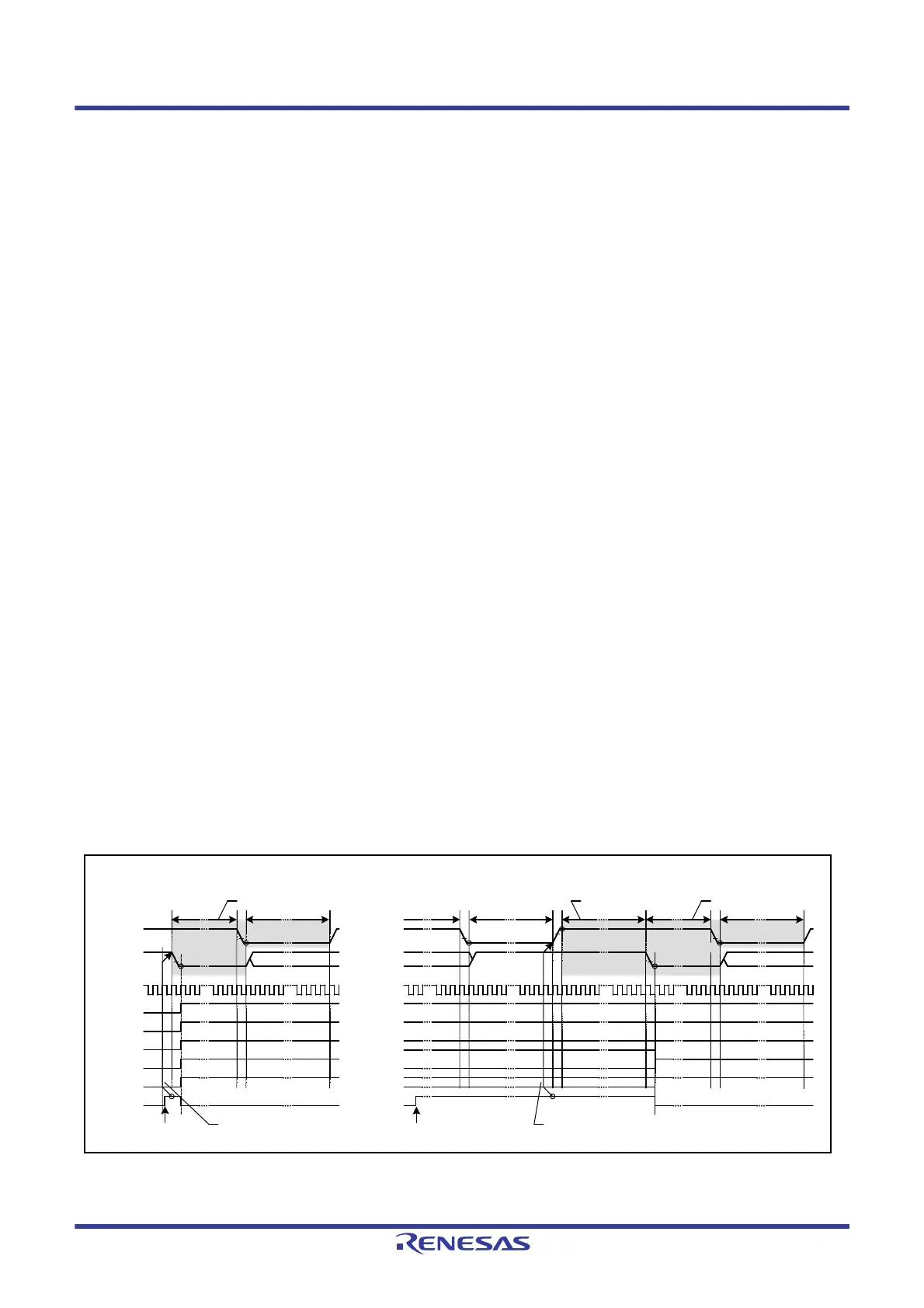

Figure 35.37 Start Condition/Restart Condition Issue Timing (ST and RS Bits)

[Start condition issuing operation]

[Restart condition issuing operation]

Write 1 to ST bit

ICBRH ICBRL

Write 1 to RS bit

ICBRH ICBRLICBRLICBRLICBRH

ACK/NACK

S8

Sr

Hold time Hold timeSetup time

Accept restart condition issuance

Accept start condition issuance

Issue start

condition

TRS

START

MST

BBSY

IIC

TDRE

ST

TRS

RS

MST

BBSY

IIC

TDRE

START

Issue restart

condition

Loading...

Loading...