R01UH0823EJ0100 Rev.1.00 Page 497 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2.9 Timer A/D Converter Start Request Cycle Set Registers A and B

(TADCORA and TADCORB)

The TADCORA and TADCORB registers specify the A/D converter start request cycle. When the MTU4.TCNT count

reaches the value in TADCORA or TADCORB, a corresponding A/D converter start request will be issued.

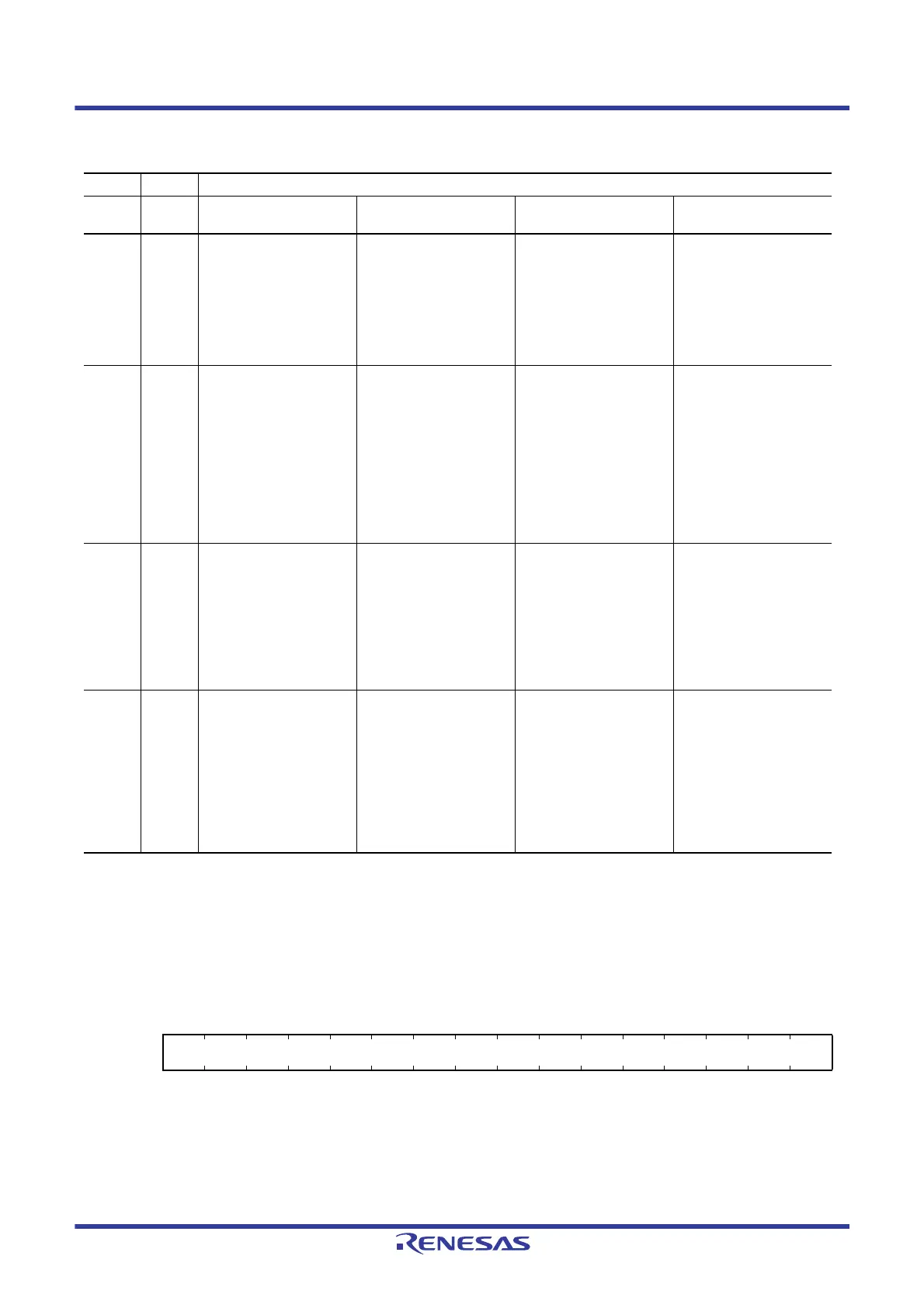

Table 23.26 Setting of Transfer Timing by TADCR.BF[1:0] Bits

Bit 15 Bit 14 Description

BF[1] BF[0]

In Complementary PWM

Mode

In Reset-Synchronized

PWM Mode In PWM Mode 1 In Normal Mode

0 0 Data is not transferred

from the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB).

Data is not transferred

from the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB).

Data is not transferred

from the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB).

Data is not transferred

from the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB).

0 1 Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) at the

crest of the MTU4.TCNT.

Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) when a

compare match occurs

between MTU3.TCNT and

MTU3.TGRA.

Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) when a

compare match occurs

between MTU4.TCNT and

MTU4.TGRA.

Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) when a

compare match occurs

between MTU4.TCNT and

MTU4.TGRA.

1 0 Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) at the

trough of the MTU4.TCNT.

Setting prohibited Setting prohibited Setting prohibited

1 1 Data is transferred from

the cycle set buffer

register

(MTU4.TADCOBRA,

MTU4.TADCOBRB) to the

cycle set register

(MTU4.TADCORA,

MTU4.TADCORB) at the

crest and trough of the

MTU4.TCNT.

Setting prohibited Setting prohibited Setting prohibited

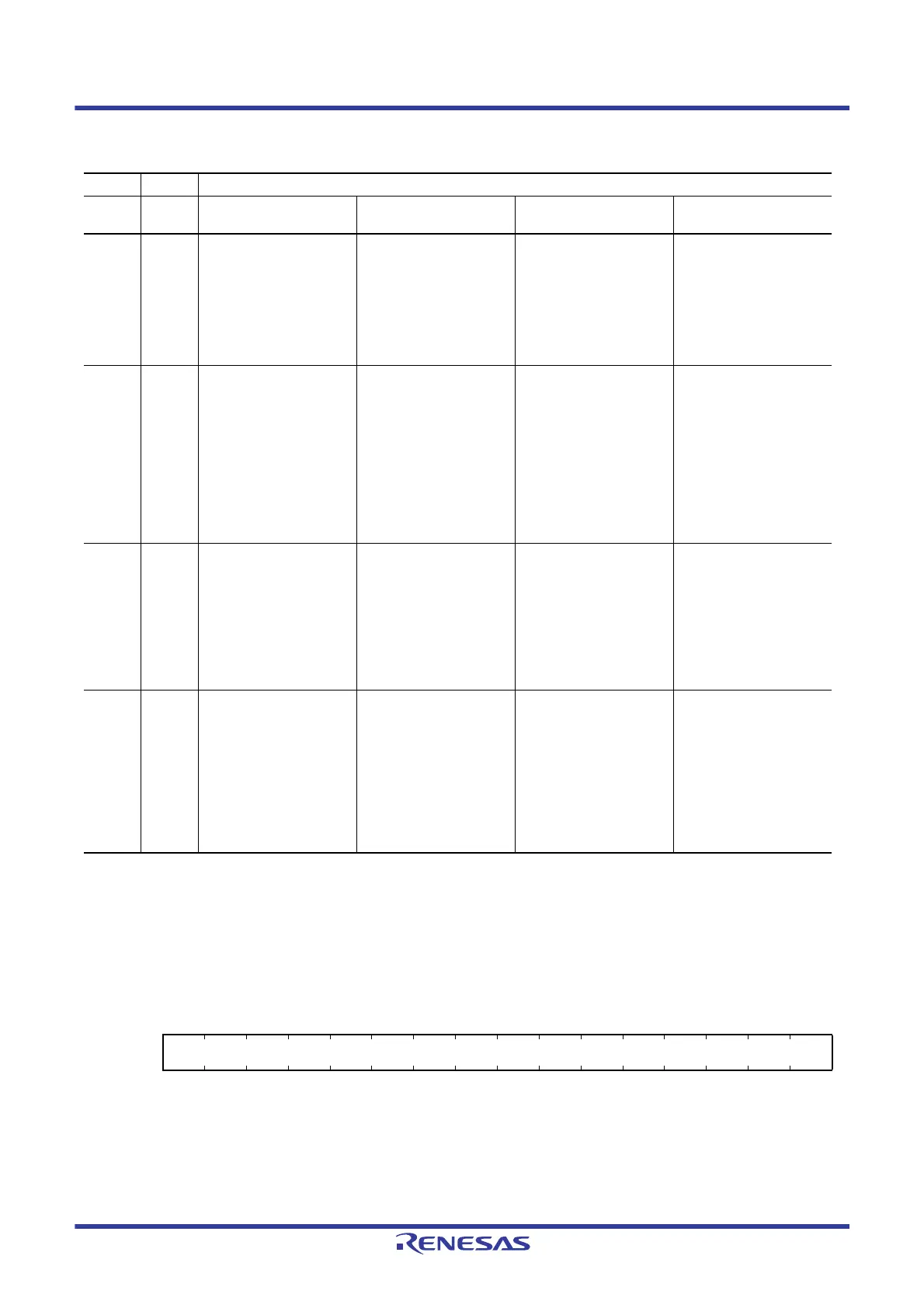

Address(es): MTU4.TADCORA 000D 0A44h, MTU4.TADCORB 000D 0A46h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

1111111111111111

Note: MTU4.TADCORA and MTU4.TADCORB must not be accessed in 8-bit units; they should be accessed in 16-bit

units.

Loading...

Loading...