R01UH0823EJ0100 Rev.1.00 Page 293 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

Note 1. An interrupt source with a smaller vector number takes precedence.

15.3.2 Fast Interrupt Vector Table

The address of the entry in the interrupt vector table that corresponds to the vector number of the fast interrupt is placed

in the fast interrupt vector register (FINTV) of the CPU.

15.3.3 Non-maskable Interrupt Vector Area

Non-maskable interrupts use the vector area in the exception vector table.

The exception vector table is allocated to the 128-byte area (4 bytes × 32 sources) beginning with the address set in the

EXTB register in the CPU. Set a multiple of 4 in the EXTB register.

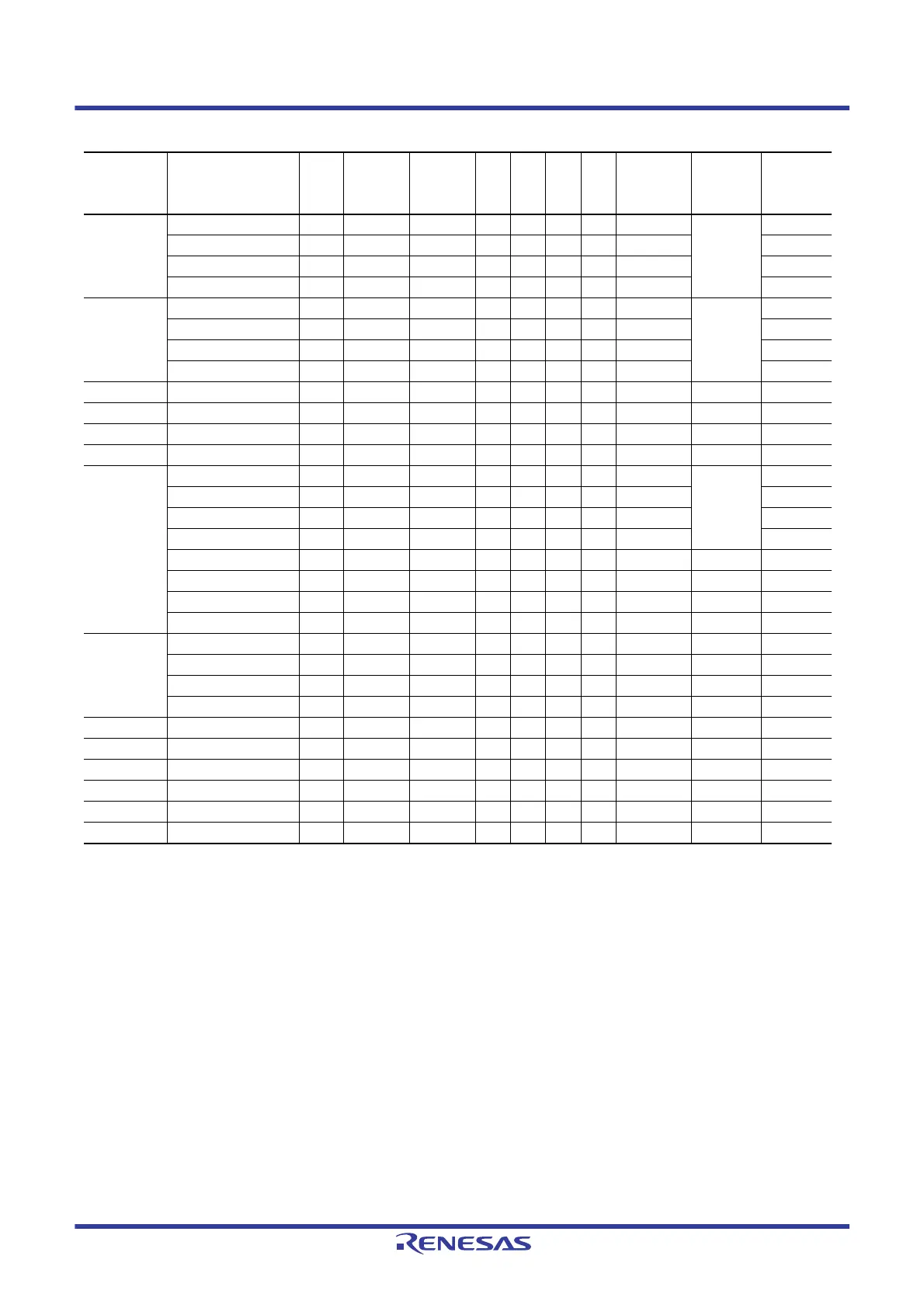

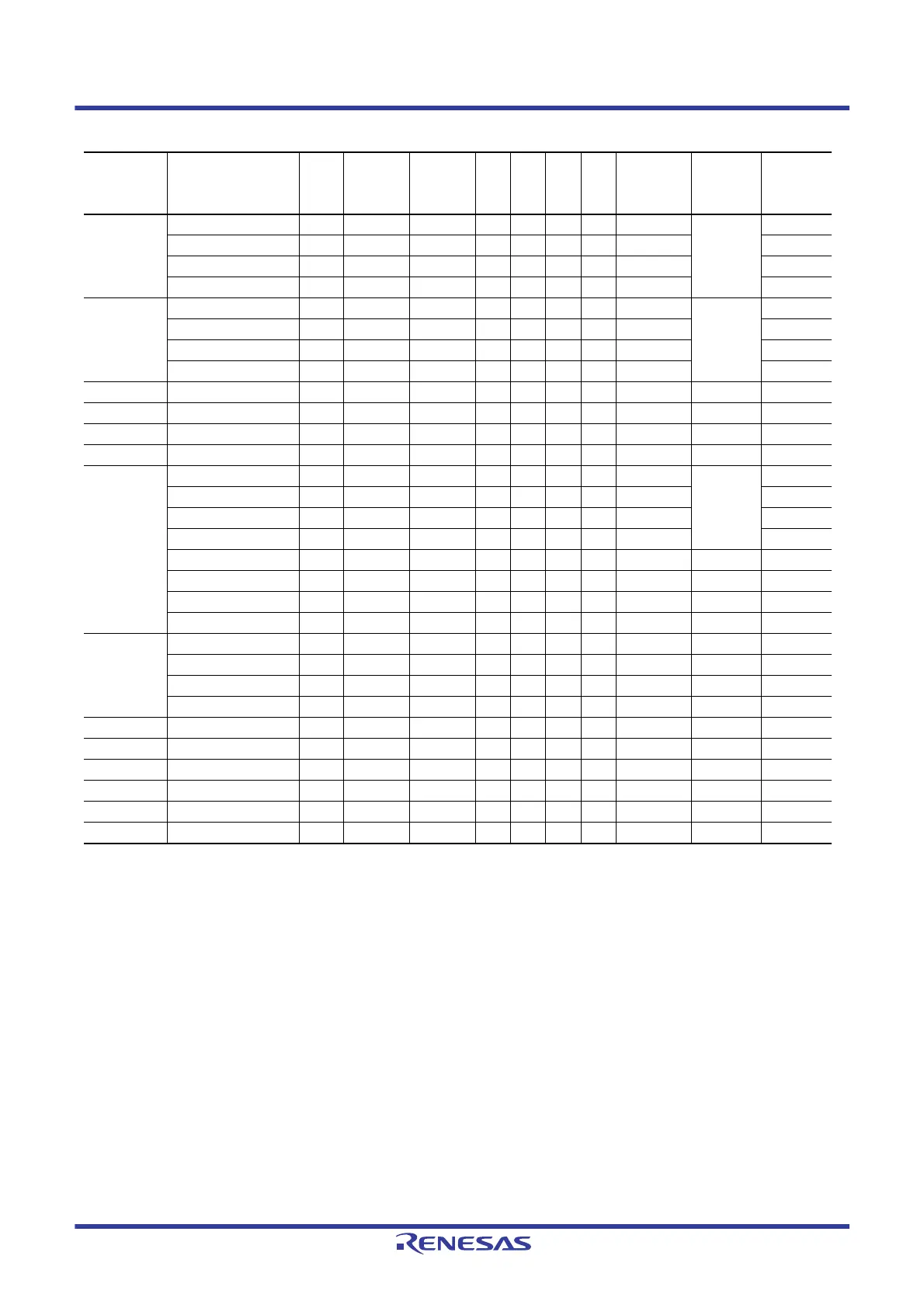

BLE ERI 226 0388h Level N/A N/A N/A IER1C.IEN2 IPR226 —

RXI 227 038Ch Edge

N/A IER1C.IEN3 DTCER227

TXI 228 0390h Edge

N/A IER1C.IEN4 DTCER228

TEI 229 0394h Level

N/A N/A N/A IER1C.IEN5 —

SCI8 ERI8 230 0398h Level

N/A N/A N/A IER1C.IEN6 IPR230 —

RXI8 231 039Ch Edge

N/A IER1C.IEN7 DTCER231

TXI8 232 03A0h Edge

N/A IER1D.IEN0 DTCER232

TEI8 233 03A4h Level

N/A N/A N/A IER1D.IEN1 —

— Reserved 234 03A8h — N/A N/A N/A N/A — — —

— Reserved 235 03ACh — N/A N/A N/A N/A — — —

— Reserved 236 03B0h — N/A N/A N/A N/A — — —

— Reserved 237 03B4h — N/A N/A N/A N/A — — —

SCI12 ERI12 238 03B8h Level

N/A N/A N/A IER1D.IEN6 IPR238 —

RXI12 239 03BCh Edge

N/A IER1D.IEN7 DTCER239

TXI12 240 03C0h Edge

N/A IER1E.IEN0 DTCER240

TEI12 241 03C4h Level

N/A N/A N/A IER1E.IEN1 —

SCIX0 242 03C8h Level

N/A N/A N/A IER1E.IEN2 IPR242 —

SCIX1 243 03CCh Level

N/A N/A N/A IER1E.IEN3 IPR243 —

SCIX2 244 03D0h Level

N/A N/A N/A IER1E.IEN4 IPR244 —

SCIX3 245 03D4h Level

N/A N/A N/A IER1E.IEN5 IPR245 —

RIIC0 EEI0 246 03D8h Level

N/A N/A N/A IER1E.IEN6 IPR246 —

RXI0 247 03DCh Edge

N/A IER1E.IEN7 IPR247 DTCER247

TXI0 248 03E0h Edge

N/A IER1F.IEN0 IPR248 DTCER248

TEI0 249 03E4h Level

N/A N/A N/A IER1F.IEN1 IPR249 —

— Reserved 250 03E8h — N/A N/A N/A N/A — — —

— Reserved 251 03ECh — N/A N/A N/A N/A — — —

— Reserved 252 03F0h — N/A N/A N/A N/A — — —

— Reserved 253 03F4h — N/A N/A N/A N/A — — —

— Reserved 254 03F8h — N/A N/A N/A N/A — — —

— Reserved 255 03FCh — N/A N/A N/A N/A — — —

Table 15.3 Interrupt Vector Table (6/6)

Source of

Interrupt

Request

Generation Name

Vector

No.*

1

Vector

Address

Offset

Form of

Interrupt

Detection

CPU

DTC

DMAC

sstb Return

IER IPR DTCER

Loading...

Loading...