R01UH0823EJ0100 Rev.1.00 Page 516 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2.29 Timer Waveform Control Registers (TWCR)

Note 1. Do not set this bit to 1 unless complementary PWM mode is selected.

Note 2. Do not set this bit to 1 unless complementary PWM mode 1 is selected.

The TWCR registers control the output waveform when synchronous counter clearing occurs in counters MTU3.TCNT

and MTU4.TCNT in complementary PWM mode and specifies whether to clear the counters at the MTU3.TGRA

compare match.

The TWCR.CCE bit and TWCR.WRE bit should be modified only while the TCNT counter stops.

WRE Bit (Initial Output Inhibition Enable)

This bit selects the waveform output when synchronous counter clearing occurs in complementary PWM mode.

The initial output is prohibited only when synchronous clearing occurs within the Tb interval at the trough in

complementary PWM mode. When synchronous clearing occurs outside this interval, the initial value specified in the

TOCR register is output regardless of the WRE bit setting. The initial value specified in the TOCR register is also output

when synchronous clearing occurs in the Tb interval at the trough immediately after counters MTU3.TCNT and

MTU4.TCNT start operation.

For the Tb interval at the trough in complementary PWM mode, refer to

Figure 23.40.

[Setting condition]

When 1 is written to the WRE bit after reading the WRE bit = 0

CCE Bit (Compare Match Clear Enable)

This bit specifies whether to clear counters at the MTU3.TGRA compare match in complementary PWM mode 1.

[Setting condition]

When 1 is written to the CCE bit after reading the CCE bit = 0

Address(es): MTU.TWCR 000D 0A60h

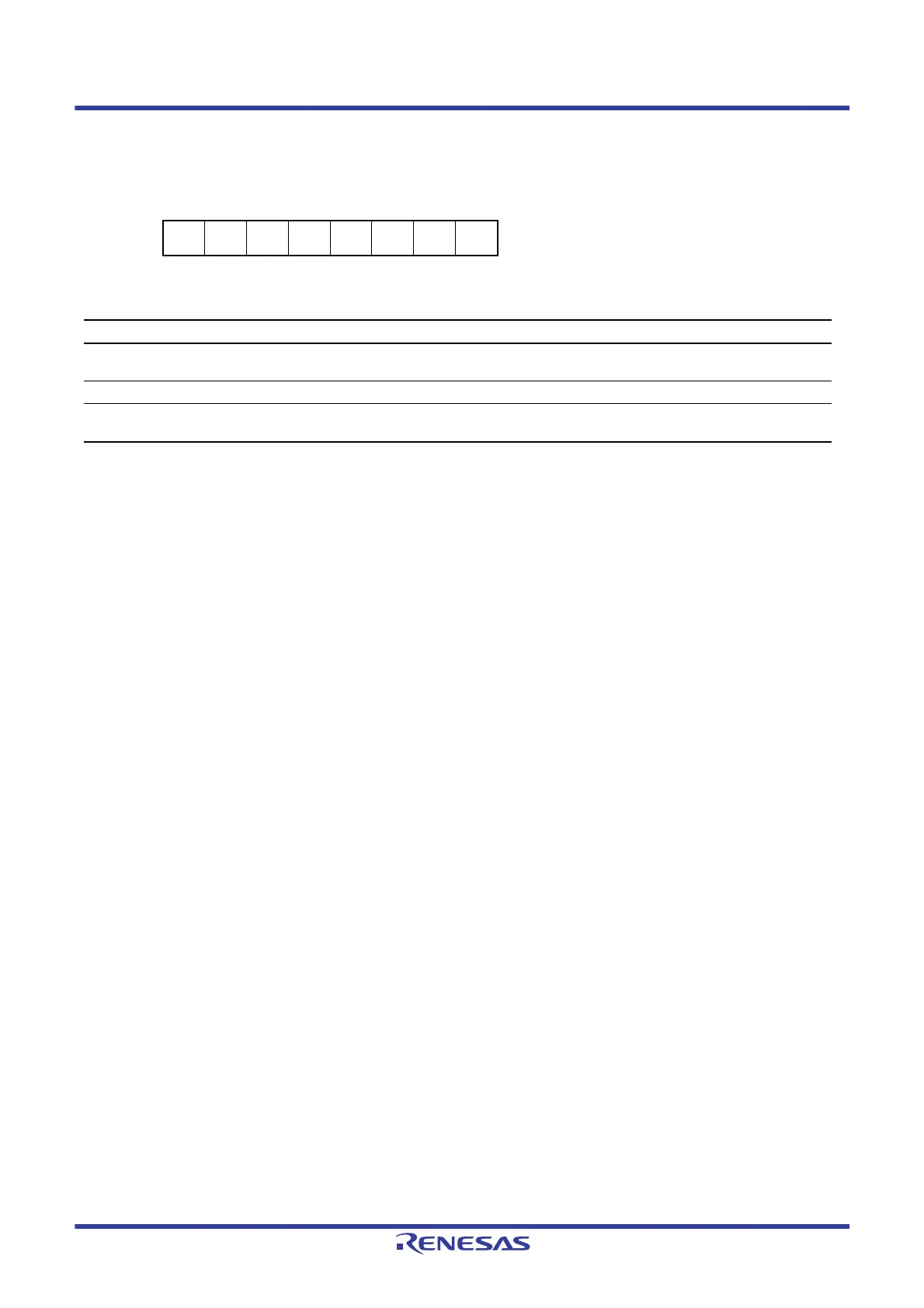

b7 b6 b5 b4 b3 b2 b1 b0

CCE——————WRE

Value after reset:

00000000

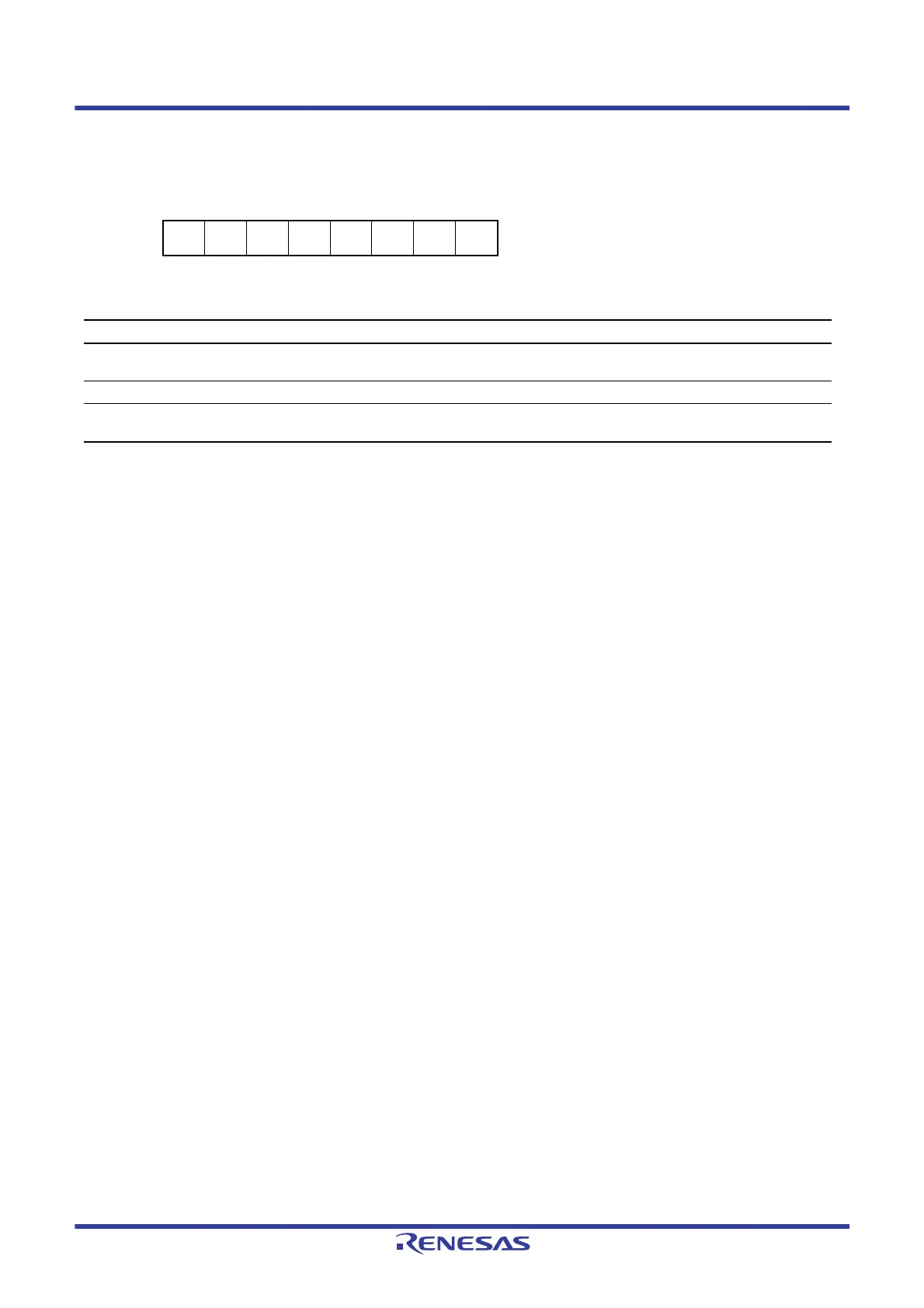

Bit Symbol Bit Name Description R/W

b0 WRE Initial Output Inhibition

Enable

0: Initial value specified in TOCR is output

1: Initial output is inhibited

R/(W)

*

1

b6 to b1 — Reserved These bits are read as 0. The write value should be 0. R/W

b7 CCE Compare Match Clear

Enable

0: Counters are not cleared at MTU3.TGRA compare match

1: Counters are cleared at MTU3.TGRA compare match

R/(W)

*

2

Loading...

Loading...