R01UH0823EJ0100 Rev.1.00 Page 476 of 1823

Jul 31, 2019

RX23W Group 23. Multi-Function Timer Pulse Unit 2 (MTU2a)

23.2 Register Descriptions

23.2.1 Timer Control Register (TCR)

x: Don’t care

The MTU has a total of five TCR registers, one each for MTU0 to MTU4.

The TCR register controls the TCNT operation for each channel. The TCR register values should be specified only while

the TCNT operation is stopped.

TPSC[2:0] Bits (Time Prescaler Select)

These bits select the TCNT count clock source. The count clock source can be selected independently for each channel.

Refer to

Table 23.6 to Table 23.9 for details.

CKEG[1:0] Bits (Clock Edge Select)

These bits select the clock edge. When the internal clock is counted at both edges, the count clock period is halved (e.g.

PCLK/4 at both edges = PCLK/2 at rising edge). If phase counting mode is used on MTU1 and MTU2, the setting of

these bits is ignored and the phase counting mode setting has priority. Internal clock edge selection is valid when the

count clock source is PCLK/4 or slower. When PCLK/1 or the overflow/underflow in another channel is selected for the

count clock source, a value can be written to these bits but counter operation compiles with the initial value.

CCLR[2:0] Bits (Counter Clear)

These bits select the TCNT counter clearing source. Refer to

Table 23.4 and Table 23.5 for details.

Address(es): MTU0.TCR 000D 0B00h, MTU1.TCR 000D 0B80h, MTU2.TCR 000D 0C00h,

MTU3.TCR 000D 0A00h, MTU4.TCR 000D 0A01h

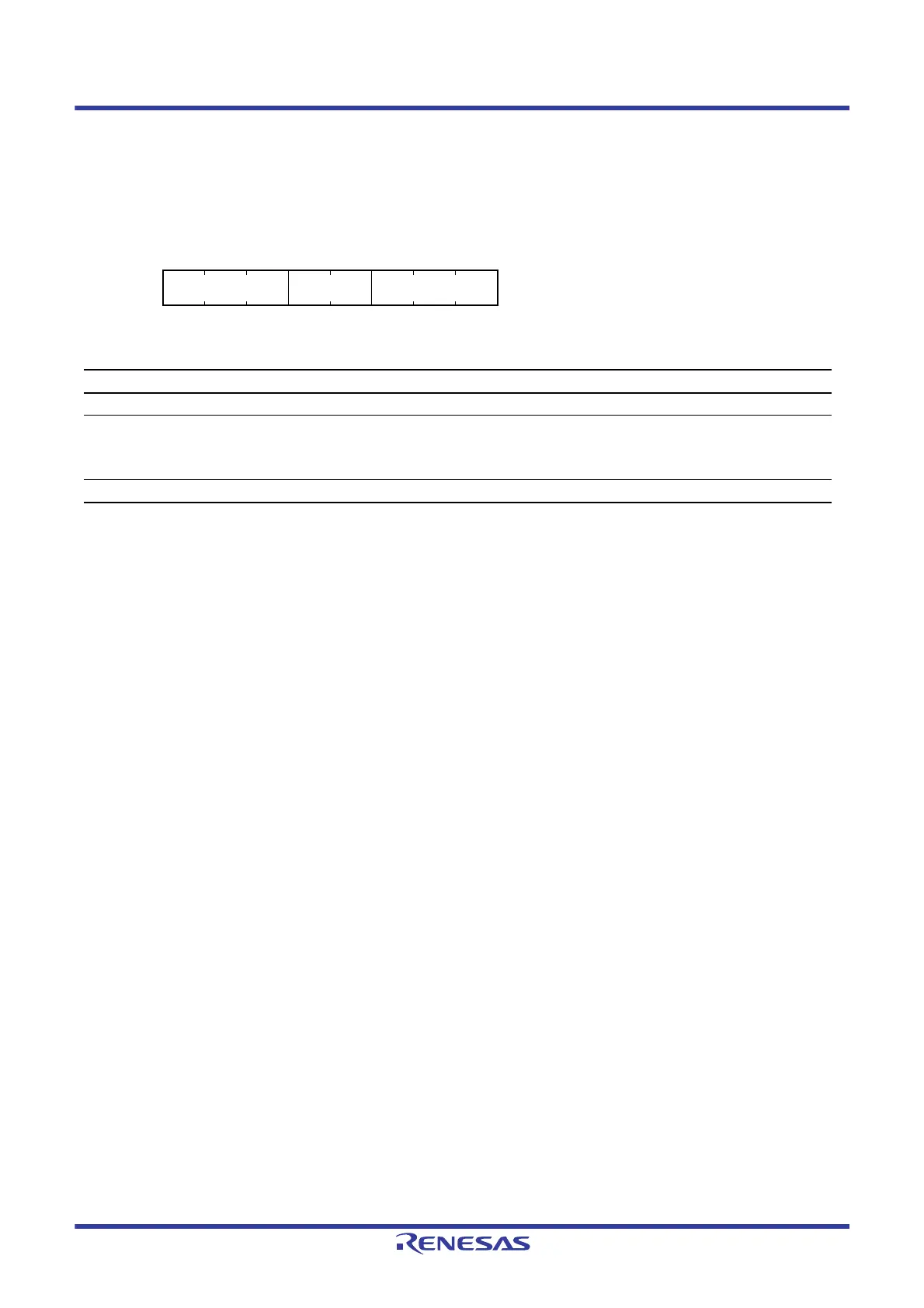

b7 b6 b5 b4 b3 b2 b1 b0

CCLR[2:0] CKEG[1:0] TPSC[2:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b2 to b0 TPSC[2:0] Time Prescaler Select Refer to Table 23.6 to Table 23.9. R/W

b4, b3 CKEG[1:0] Clock Edge Select

b4 b3

0 0: Count at rising edge

0 1: Count at falling edge

1 x: Count at both edges

R/W

b7 to b5 CCLR[2:0] Counter Clear Refer to Table 23.4 and Table 23.5. R/W

Loading...

Loading...