R01UH0823EJ0100 Rev.1.00 Page 772 of 1823

Jul 31, 2019

RX23W Group 28. Realtime Clock (RTCe)

28.2.9 Second Alarm Register (RSECAR)/Binary Counter 0 Alarm Register

(BCNT0AR)

(1) In calendar count mode:

The RSECAR register is an alarm register corresponding to the BCD-coded second counter RSECCNT. When the ENB

bit is set to 1, the RSECAR value is compared with the RSECCNT value. From among the alarm registers (RSECAR,

RMINAR, RHRAR, RWKAR, RDAYAR, RMONAR, and RYRAREN), only those selected with the ENB bits set to 1

are compared with the corresponding counters. When the respective values all match, the IR flag corresponding to the

ALM interrupt is set to 1.

RSECAR values from 00 through 59 (in BCD) can be specified; if a value outside of this range is specified, the RTC

does not operate correctly.

After writing to the RSECAR register, confirm that its value has actually changed before proceeding with further

processing. Refer to

section 28.6.5, Notes When Writing to and Reading from Registers for notes on accessing

registers.

This register is set to 00h by an RTC software reset.

(2) In binary count mode:

The BCNT0AR counter is a readable/writable alarm register corresponding to 32-bit binary counter b7 to b0.

This register is set to 00h by an RTC software reset.

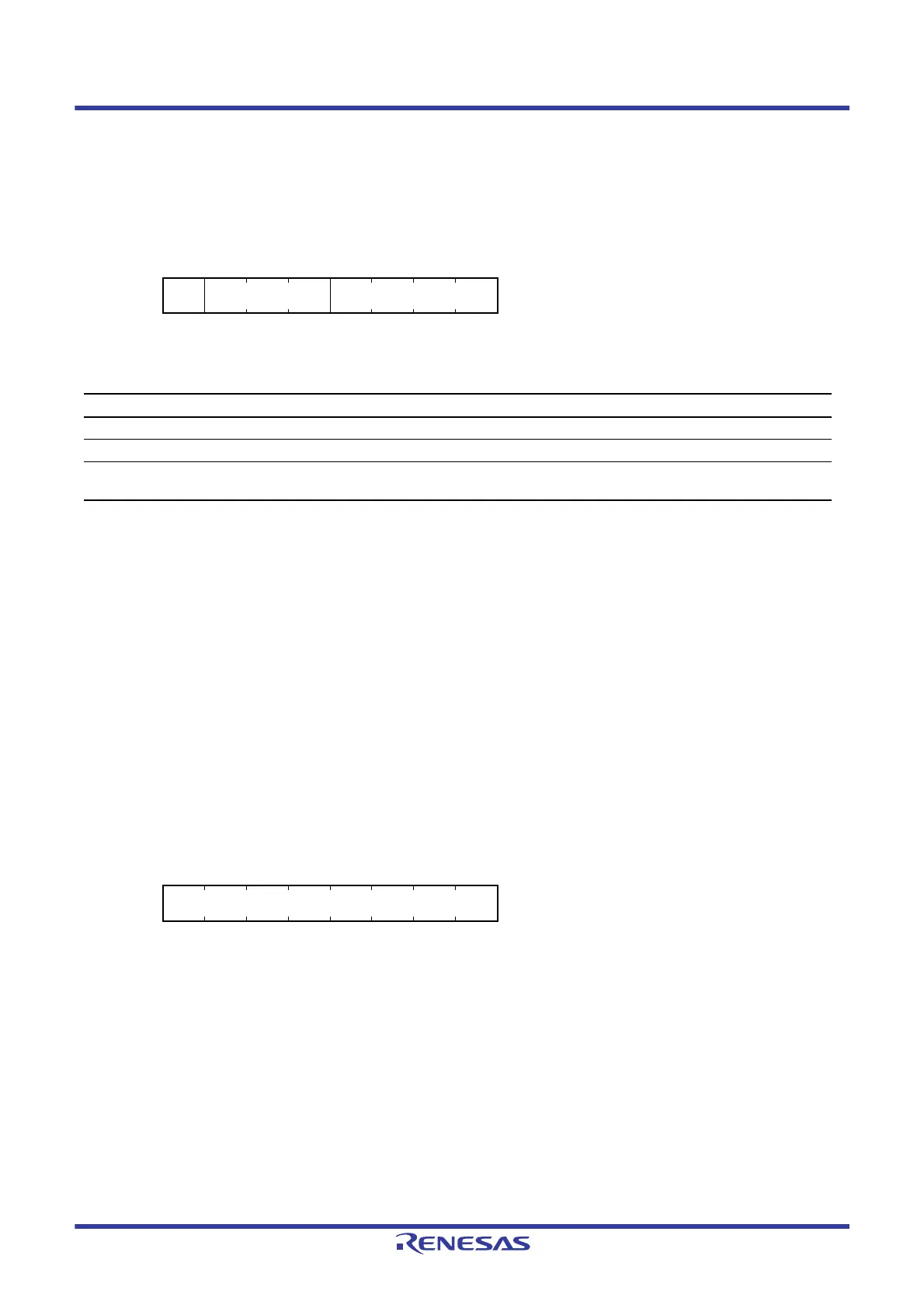

Address(es): RTC.RSECAR 0008 C410h

b7 b6 b5 b4 b3 b2 b1 b0

ENB SEC10[2:0] SEC1[3:0]

Value after reset:

xxxxxxxx

x: Undefined

Bit Symbol Bit Name Description R/W

b3 to b0 SEC1[3:0] 1 Second Value for the ones place of seconds R/W

b6 to b4 SEC10[2:0] 10 Seconds Value for the tens place of seconds R/W

b7 ENB ENB 0: The register value is not compared with the RSECCNT counter value.

1: The register value is compared with the RSECCNT counter value.

R/W

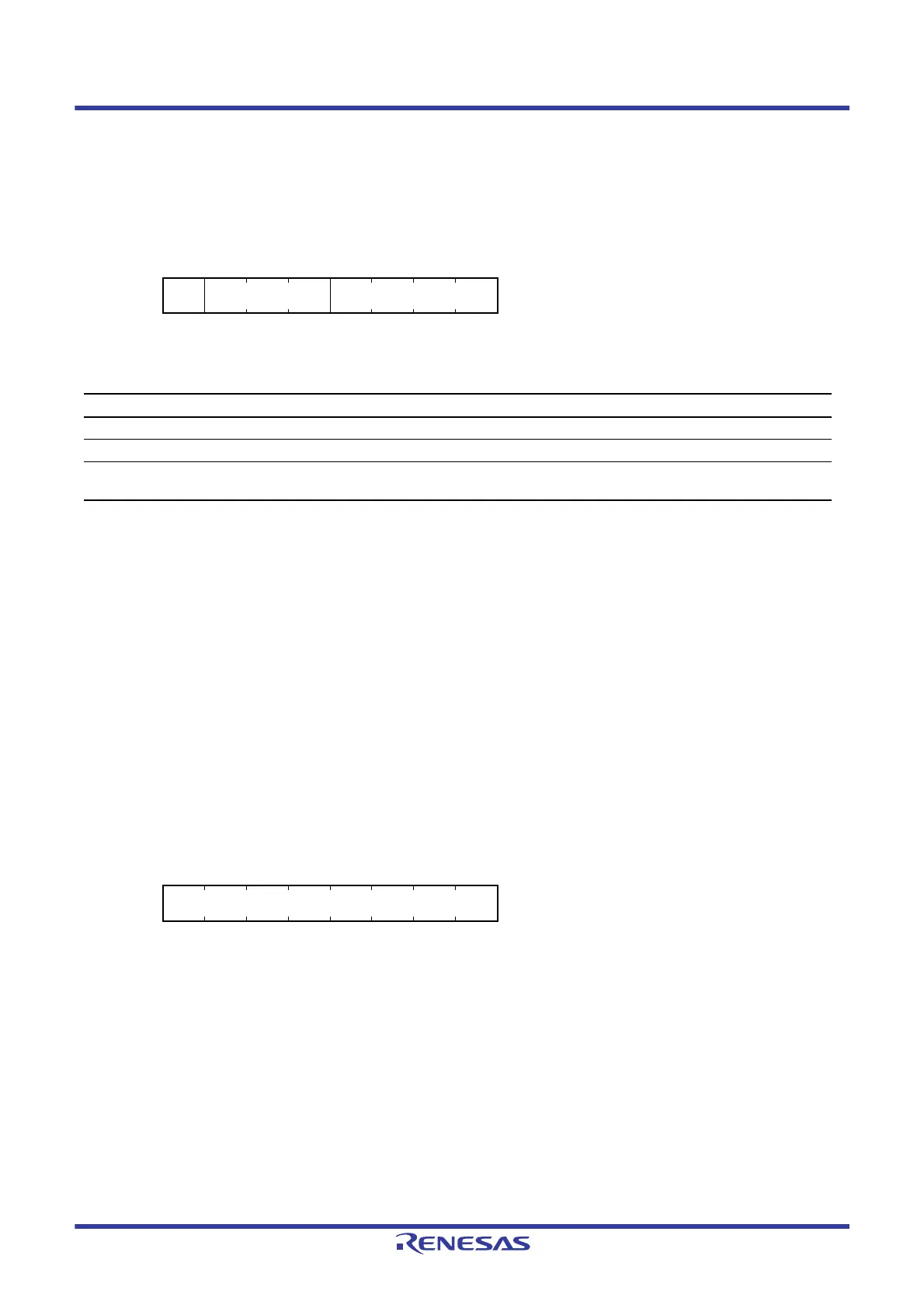

Address(es): RTC.BCNT0AR 0008 C410h

b7 b6 b5 b4 b3 b2 b1 b0

BCNTAR[7:0]

Value after reset:

xxxxxxxx

x: Undefined

Loading...

Loading...