R01UH0823EJ0100 Rev.1.00 Page 393 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

Note 1. The transfer counters used depend on transfer modes as follows:

Normal transfer mode: CRA register

Repeat transfer mode: CRAL register

Block transfer mode: CRB register

Note 2. On completion of data transfer, the counters operate as follows:

1 → 0 in normal and block transfer modes

1 → CRAH in repeat transfer mode

(1 →

) in the table indicates both of the two operations above.

Note 3. Chain transfer can be selected for the second or subsequent transfers. The condition combination of “second transfer and the

CHNE bit is 1” is omitted.

19.4.1 Transfer Information Read Skip Function

Reading of DTC vector and transfer information can be skipped by the setting of the DTCCR.RRS bit.

When a DTC transfer request is accepted, the current DTC vector number is compared with the DTC vector number in

the previous data transfer. When these vector numbers match and the RRS bit is 1, the DTC does not read the DTC vector

and transfer information, and transfers data according to the transfer information remained in the DTC.

However, when the previous transfer was chain transfer, the DTC vector and transfer information are read. Furthermore,

when the transfer counter (CRA register) became 0 during the previous normal transfer and when the transfer counter

(CRB register) became 0 during the previous block transfer, transfer information is read regardless of the value of the

RRS bit.

Figure 19.13 shows an example of transfer information read skip.

When updating the vector table and transfer information, set the RRS bit to 0, update the vector table and transfer

information, and then set the RRS bit to 1. Setting the RRS bit to 0 discards the vector numbers retained in the DTC. The

updated DTC vector table and transfer information are read in the next data transfer.

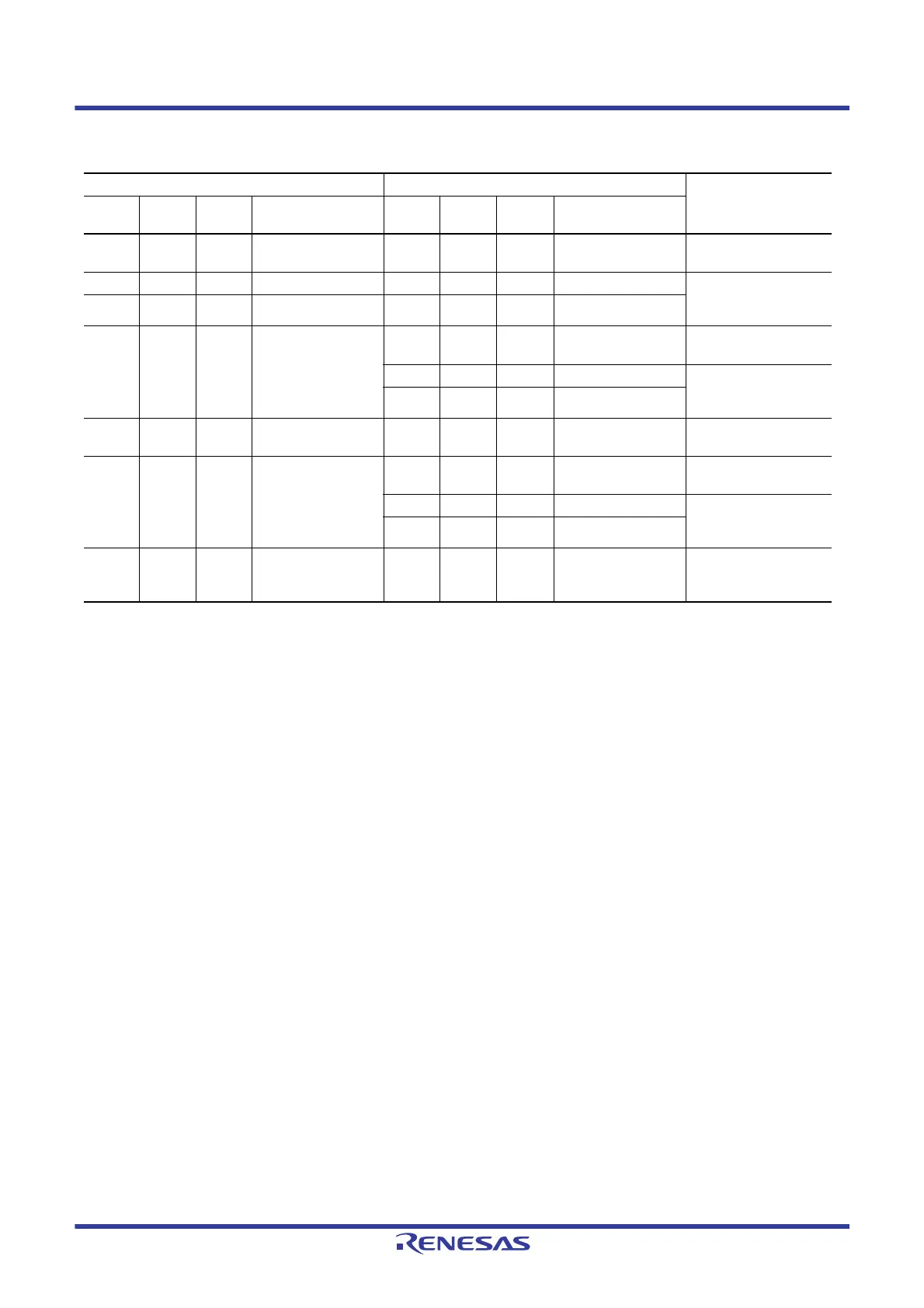

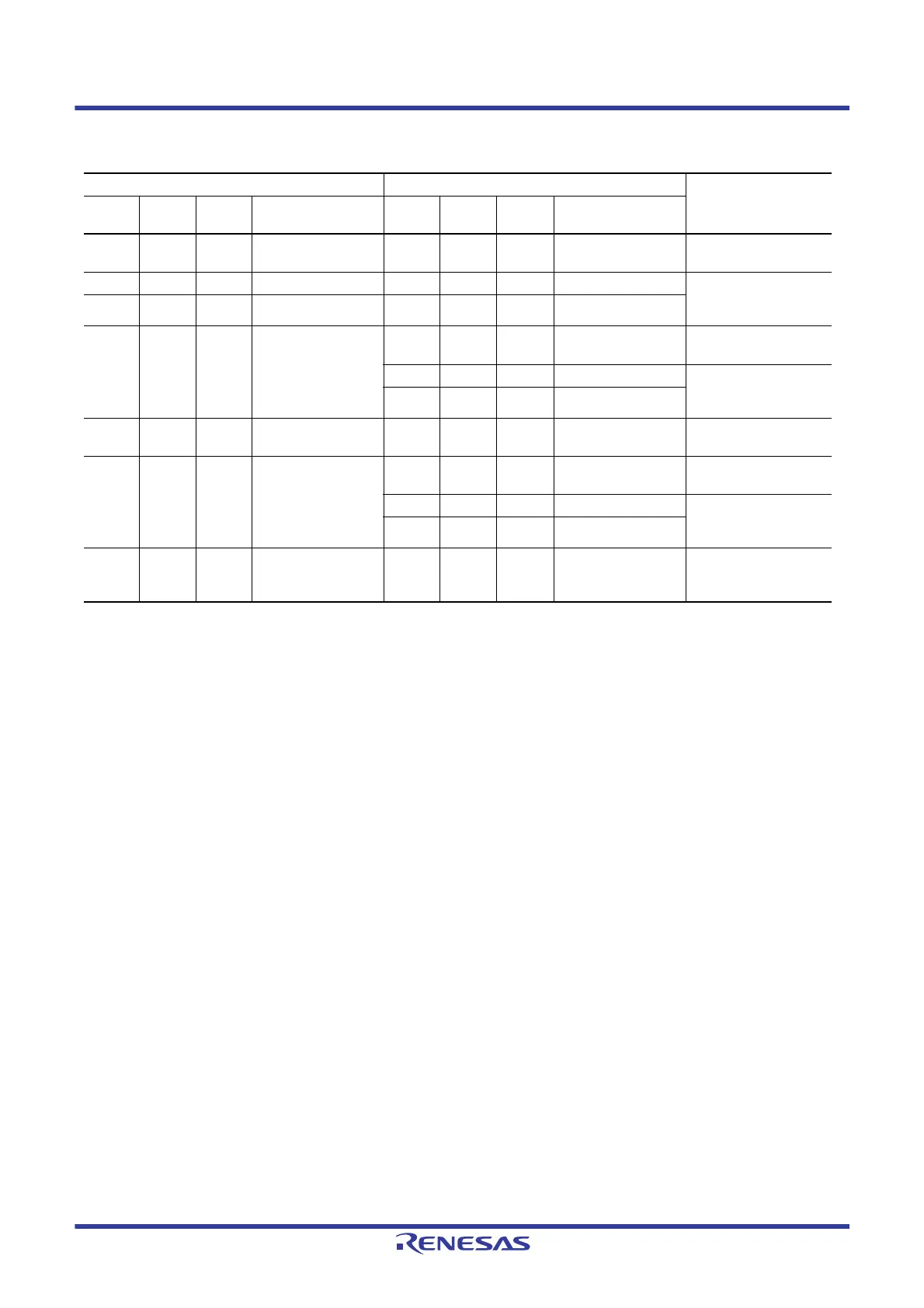

Table 19.3 Chain Transfer Conditions

First Transfer Second Transfer*

3

Data Transfer

CHNE

Bit

CHNS

Bit

DISEL

Bit

Transfer

Counter*

1,

*

2

CHNE

Bit

CHNS

Bit

DISEL

Bit

Transfer

Counter*

1,

*

2

0 — 0 Other than (1 → 0) — — — — Ends after the first

transfer

0 — 0 (1 → 0) — — — — Ends after the first

transfer with an interrupt

request to the CPU

0—1— ————

1 0 — — 0 — 0 Other than (1 → 0) Ends after the second

transfer

0 — 0 (1 → 0) Ends after the second

transfer with an interrupt

request to the CPU

0—1—

1 1 0 Other than (1 →

) — — — — Ends after the first

transfer

11—(1 →

) 0 — 0 Other than (1 → 0) Ends after the second

transfer

0 — 0 (1 → 0) Ends after the second

transfer with an interrupt

request to the CPU

0—1—

1 1 1 Other than (1 →

) — — — — Ends after the first

transfer with an interrupt

request to the CPU

Loading...

Loading...