R01UH0823EJ0100 Rev.1.00 Page 294 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.4 Interrupt Operation

The interrupt controller performs the following processing.

Detecting interrupts

Enabling and disabling interrupts

Selecting interrupt request destinations (CPU interrupt, DTC trigger, or DMAC trigger)

Determining priority

15.4.1 Detecting Interrupts

Interrupt requests are detected in either of two ways: the detection of edges of the interrupt signal or the detection of a

level of the interrupt signal.

Edge detection or level detection is selected for the IRQi pins (i = 0, 1, and 4 to 7) as external interrupt requests by the

setting of the IRQMD[1:0] bits in IRQCRi.

For interrupts from peripheral modules, either edge detection or level detection is determined per interrupt source.

For the correspondence between interrupt sources and methods of detection, see

Table 15.3, Interrupt Vector Table.

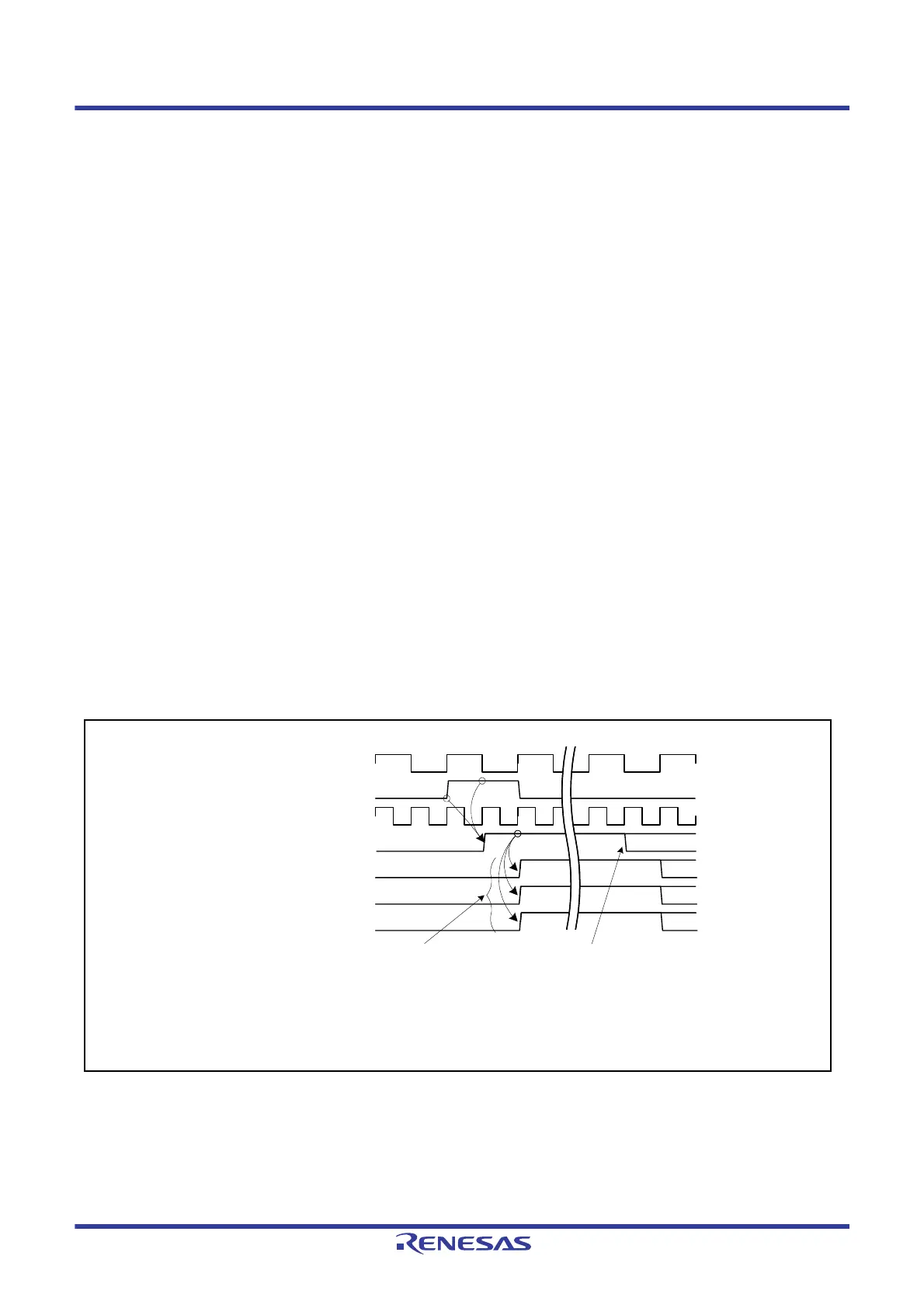

15.4.1.1 Operation of Status Flags for Edge-Detected Interrupts

Figure 15.2 shows the operation of the IR flag in IRn (n = interrupt vector number) in the case of edge detection of an

interrupt from a peripheral module or on an external pin.

The IR flag in IRn is set to 1 immediately after the transition of the interrupt signal due to generation of the interrupt. If

the CPU is the request destination for the interrupt, the IR flag is automatically cleared to 0 on acceptance of the

interrupt. If the DMAC or DTC is the request destination for the interrupt, the IRn.IR flag operation differs according to

the DMAC/DTC transfer settings and transfer count. For details, see

Table 15.4, Operation When Starting the

DMAC/DTC

.

Figure 15.2 IRn.IR Flag Operation for Edge Detection Interrupts

System clock

Interrupt signal

IRn.IR flag

Peripheral module clock

CPU interrupt request

DTC transfer request

DMA transfer request

*1 *2

Note 1. One of the following requests is issued: CPU interrupt request, DTC transfer request, and DMA transfer request.

For details of the setting, see section 15.4.3, Selecting Interrupt Request Destinations.

Note 2. When the CPU interrupt request is specified, this flag is set to 0 on acceptance of a CPU interrupt. For the timing of 0

setting at the DTC transfer request or DMA transfer request, see Table 15.4, Operation When Starting the DMAC/

DTC.

Loading...

Loading...