R01UH0823EJ0100 Rev.1.00 Page 1327 of 1823

Jul 31, 2019

RX23W Group 37. Serial Sound Interface (SSI)

37.3.6 Receive Operation

Like transmission, reception can be controlled either by DMA/DTC transfer or interrupt.

Figure 37.20 and Figure 37.21 show the flow of operation.

When stopping reception, set the SSICR.REN bit to 0 and continue to supply the clock

*

1

until the SSISR.IIRQ flag

becomes 1 (in idle state).

Note 1. Input clock from the SSISCK0 pin when SSICR.SCKD bit = 0.

Master clock when SSICR.SCKD bit = 1.

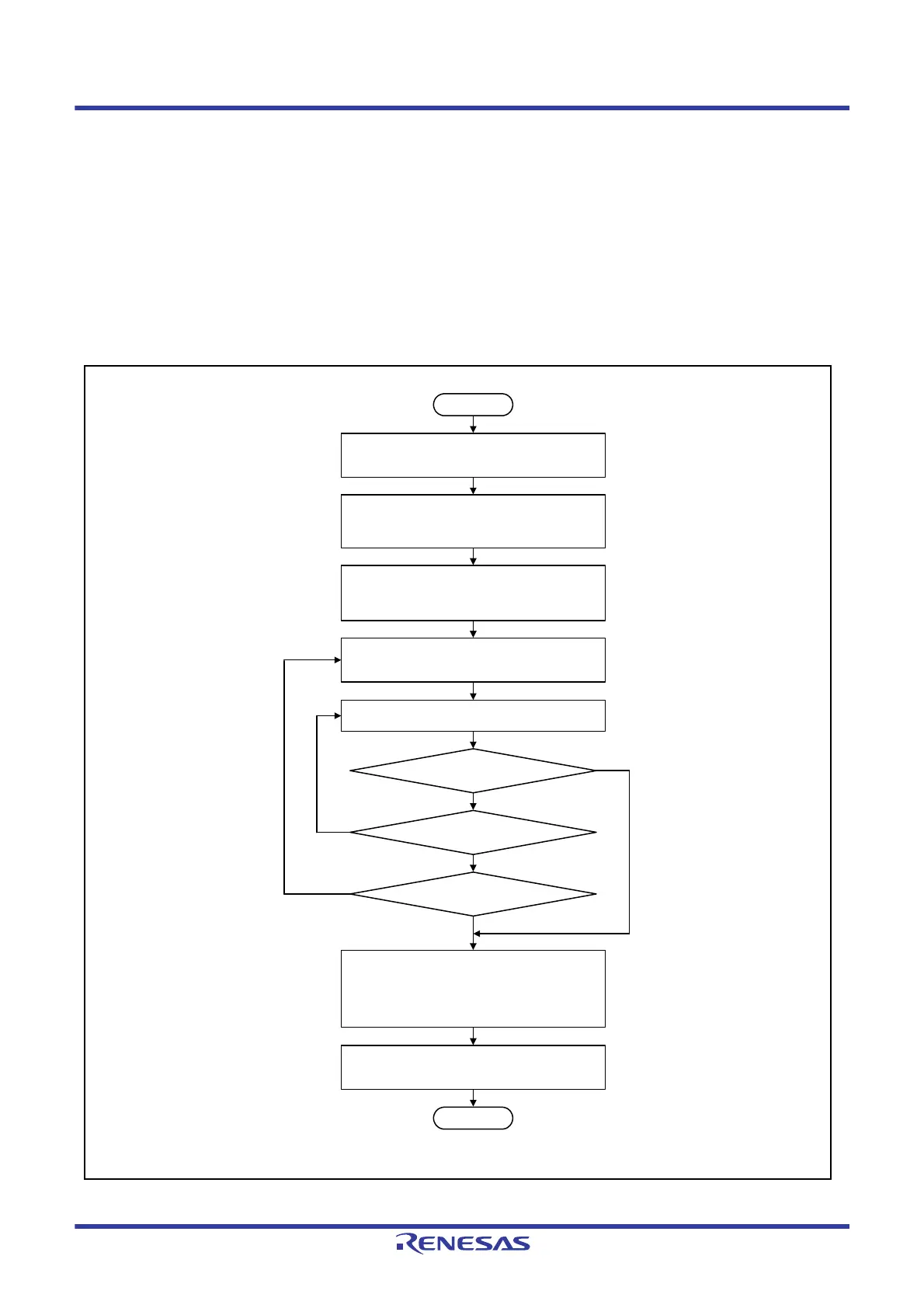

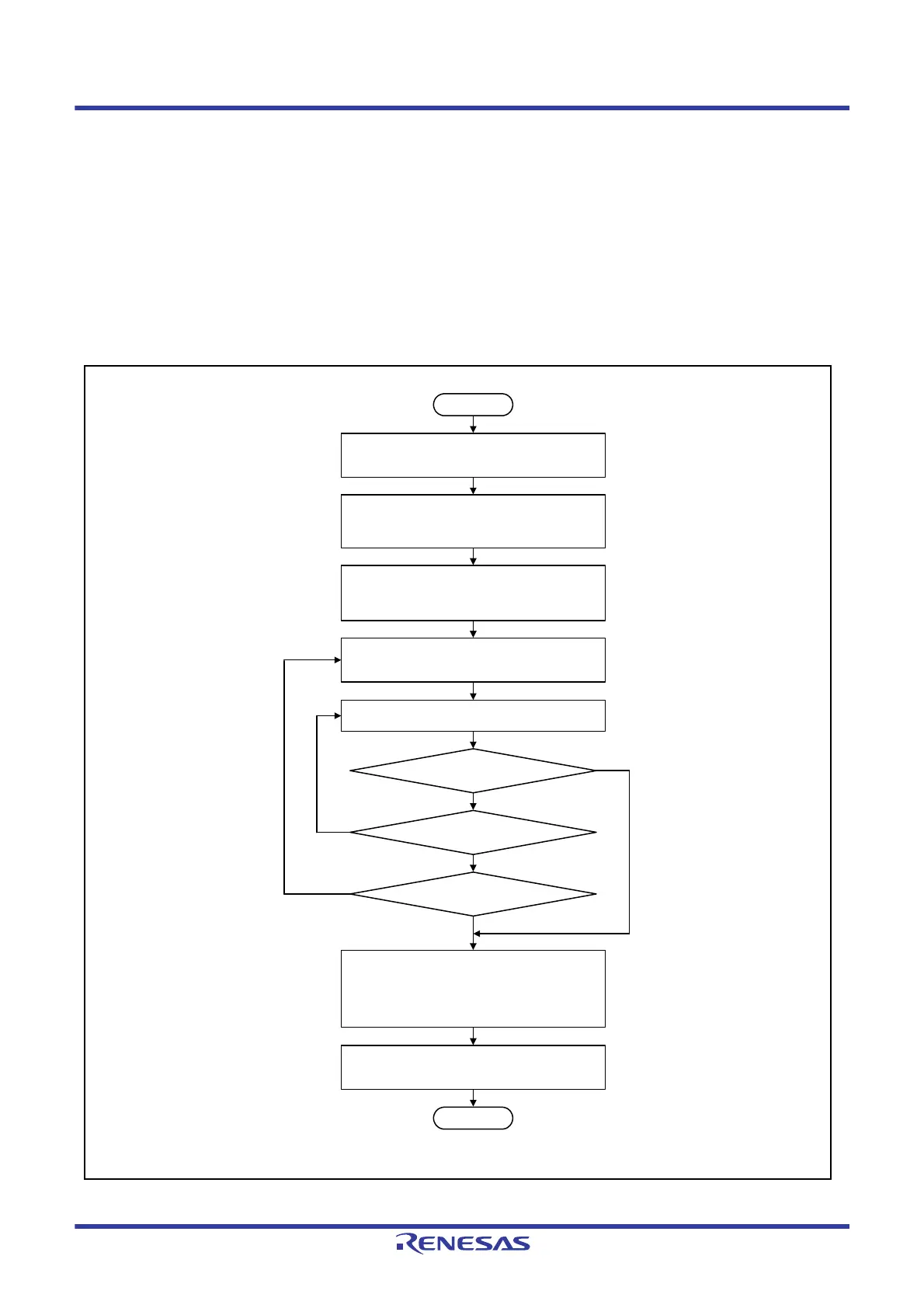

(1) Reception Using the DMAC/DTC

Figure 37.20 Reception Using the DMAC/DTC

Start

Set the SSIFCR.AUCKE bit to 1 in master

mode.

Set the SSICR register

configuration bits.

Wait for an interrupt.

Error interrupt?

More data to be received?

Wait for an idle interrupt

from this module

End

*1

No

Yes

No

Yes

No

Yes

Setup and enable the DMAC/DTC,

enable an error interrupt,

enable receive operation.

End of DMA/DTC transfer?

Note 1. If an error interrupt (underflow/overflow) occurs, go back to the start in the flowchart again.

Enable a receive interrupt,

enable the DMAC/DTC

Disable receive operation,

disable the DMAC/DTC,

disable an error interrupt,

enable an idle interrupt.

Loading...

Loading...