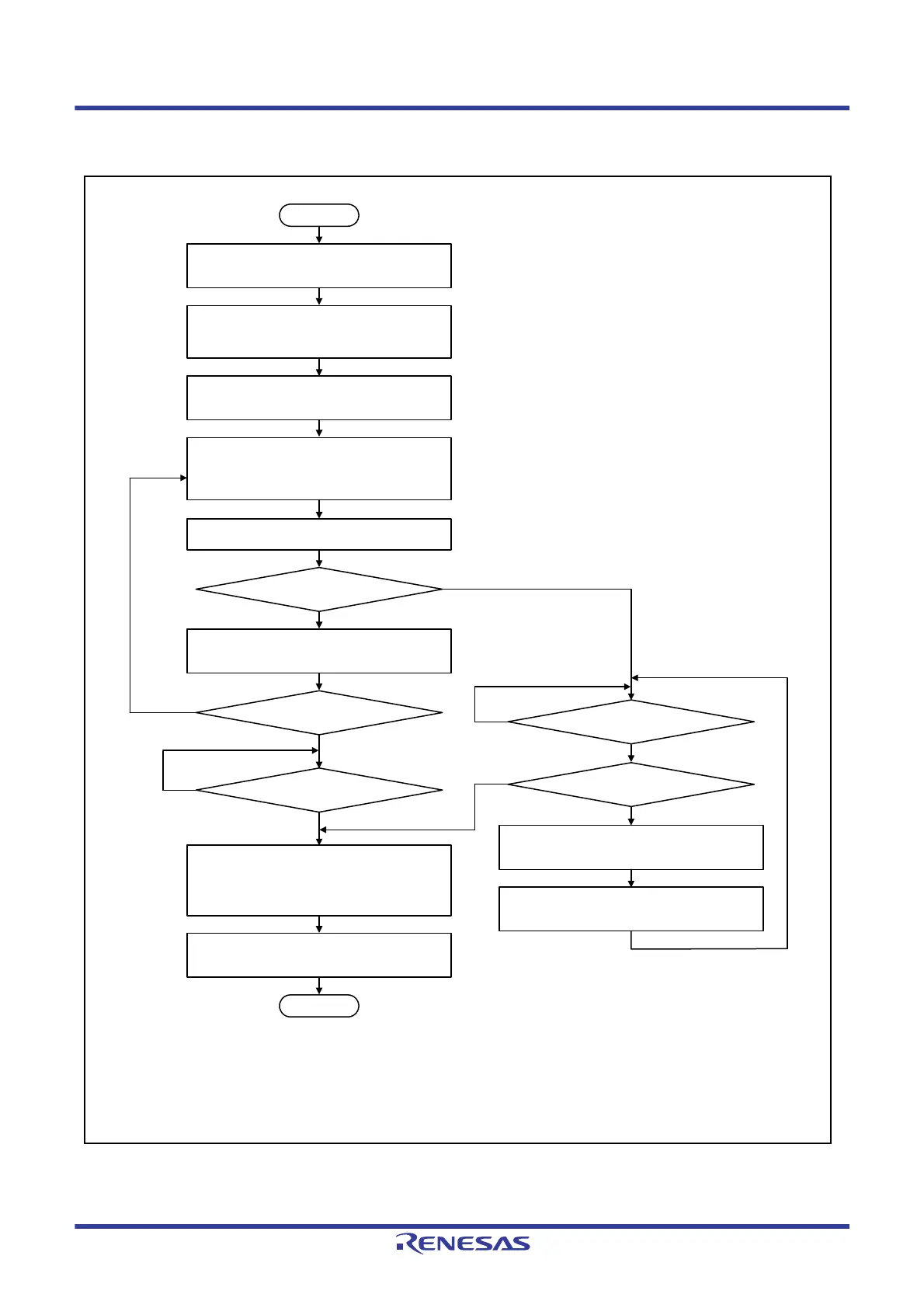

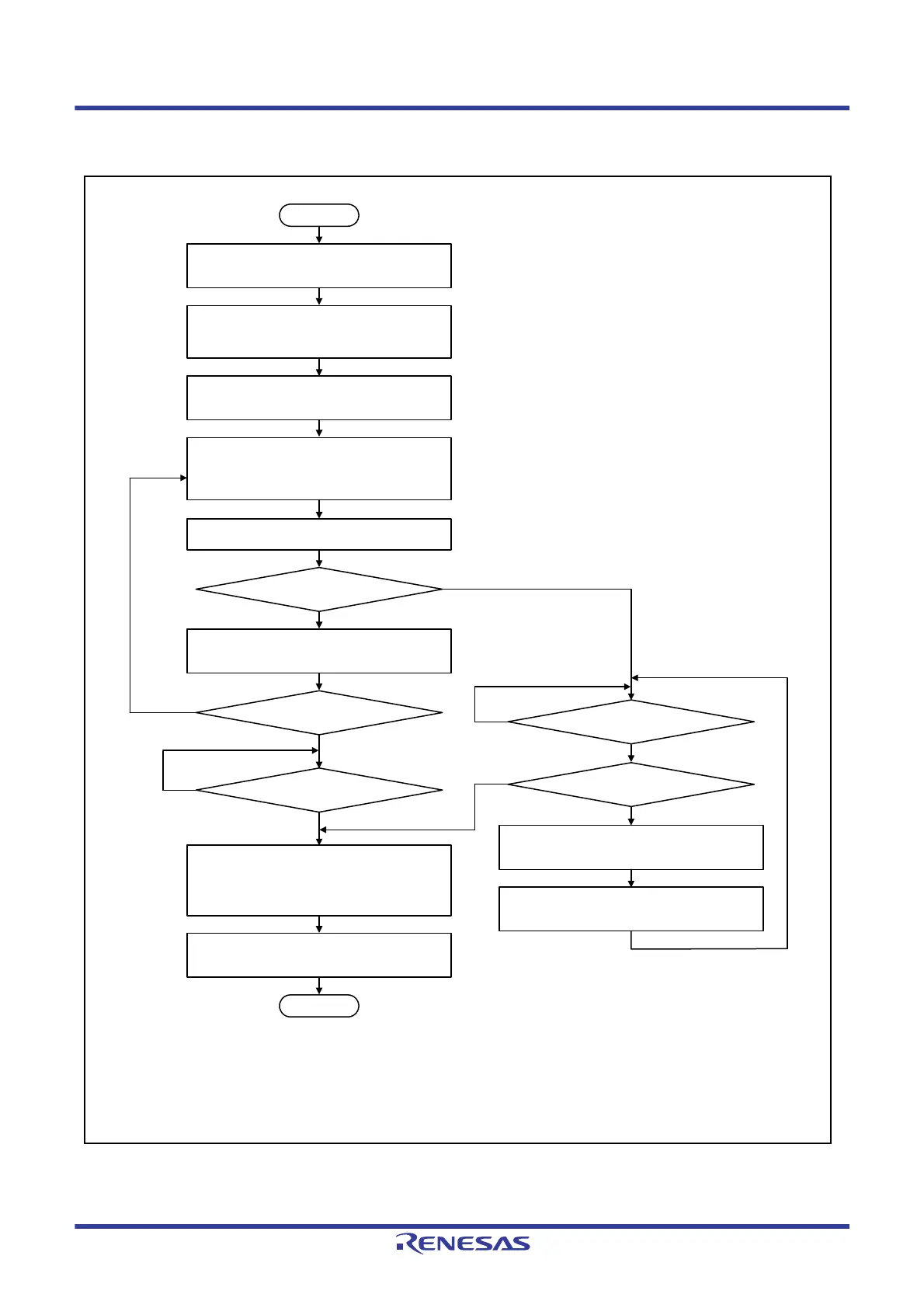

Start

Set the SSIFCR.AUCKE bit to 1 in master

mode.

Set the SSICR register

configuration bits.

Enable an error interrupt,

enable a transmit interrupt,

enable transmit operation.

Setup the interrupt controller.

Wait for an interrupt.

Error interrupt?

More data to be sent?

Disable transmit operation,

disable an error interrupt,

enable an idle interrupt.

Wait for an idle interrupt

from this module

End

*1

No

No

Yes

Yes

Transmit underflow occurred?

*3

Yes

No

Transmit underflow occurred?

*3

Yes

No

TSWNO = 0?

No

Write 32-bit 0-data to the SSIFTDR register.

Clear the transmit underflow error interrupt

status flag.

Yes

Write transmit data

*2

,

clear the SSIFSR.TDE flag

Note 1. When restarting transmission after transmit operation is disabled (TEN = 0) while WS continue mode is

disabled, execute a software reset and go back to the start of the flowchart again.

Note 2. Write transmit data in 64-bit units regardless of the data word setting.

Note 3. Stop writing transmit data to the SSIFTDR register and wait until a transmit underflow occurs.

During transmit underflow, the last data input to SSIFTDR register is continuously transmitted until the module is

in the idle state.

Loading...

Loading...