R01UH0823EJ0100 Rev.1.00 Page 758 of 1823

Jul 31, 2019

RX23W Group 27. Compare Match Timer (CMT)

27.3 Operation

27.3.1 Periodic Count Operation

When an frequency dividing clock is selected by the CMCR.CKS[1:0] bits and the CMSTRm.STRn (m = 0, 1; n = 0 to 3)

bit is set to 1, the CMCNT counter starts counting up using the selected clock.

When the value in the counter and the value in the register match, a compare match interrupt (CMIn) (n = 0 to 3) is

generated. The CMCNT counter then starts counting up again from 0000h.

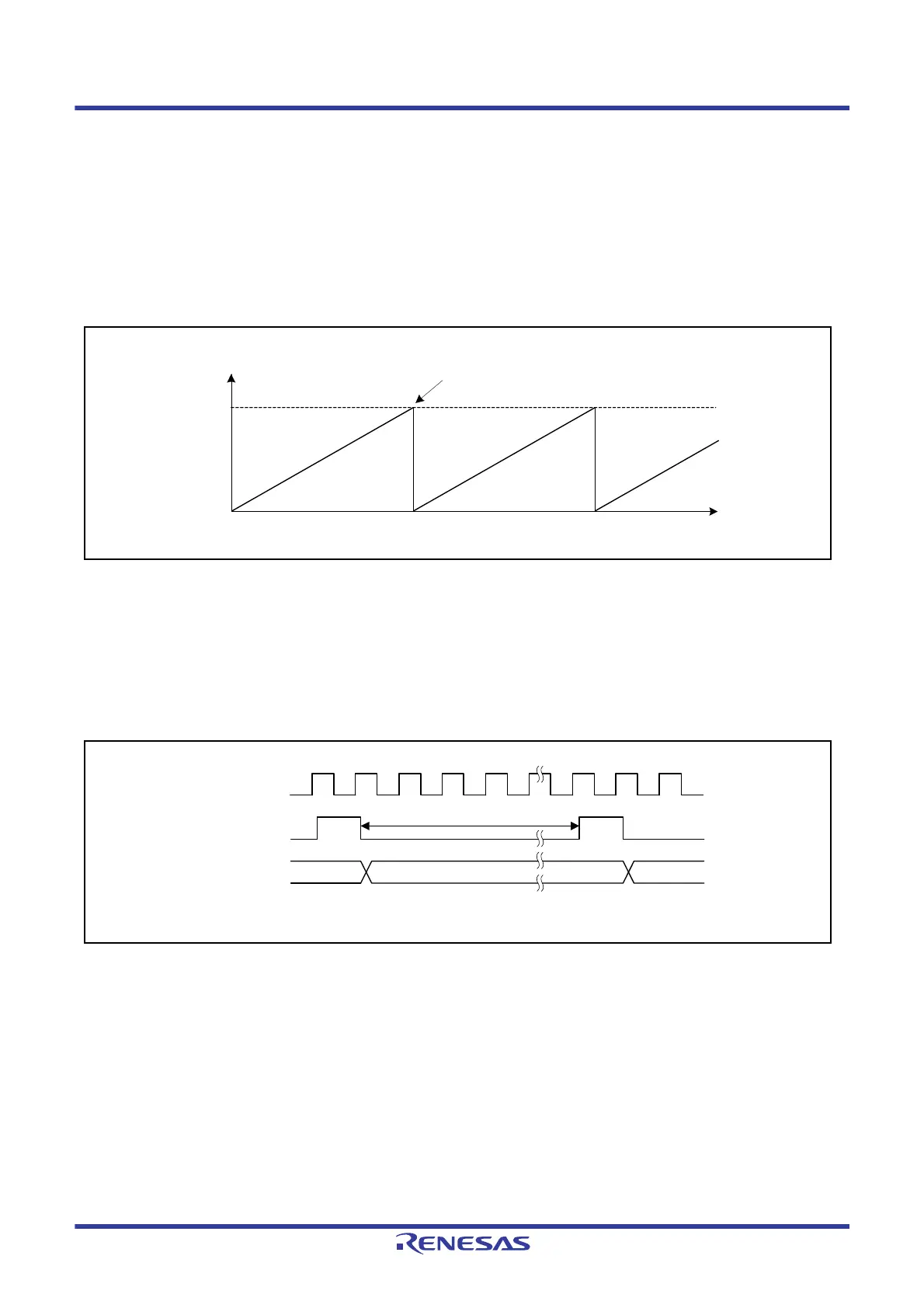

Figure 27.2 shows the operation of the

CMCNT counter.

Figure 27.2 CMCNT Counter Operation

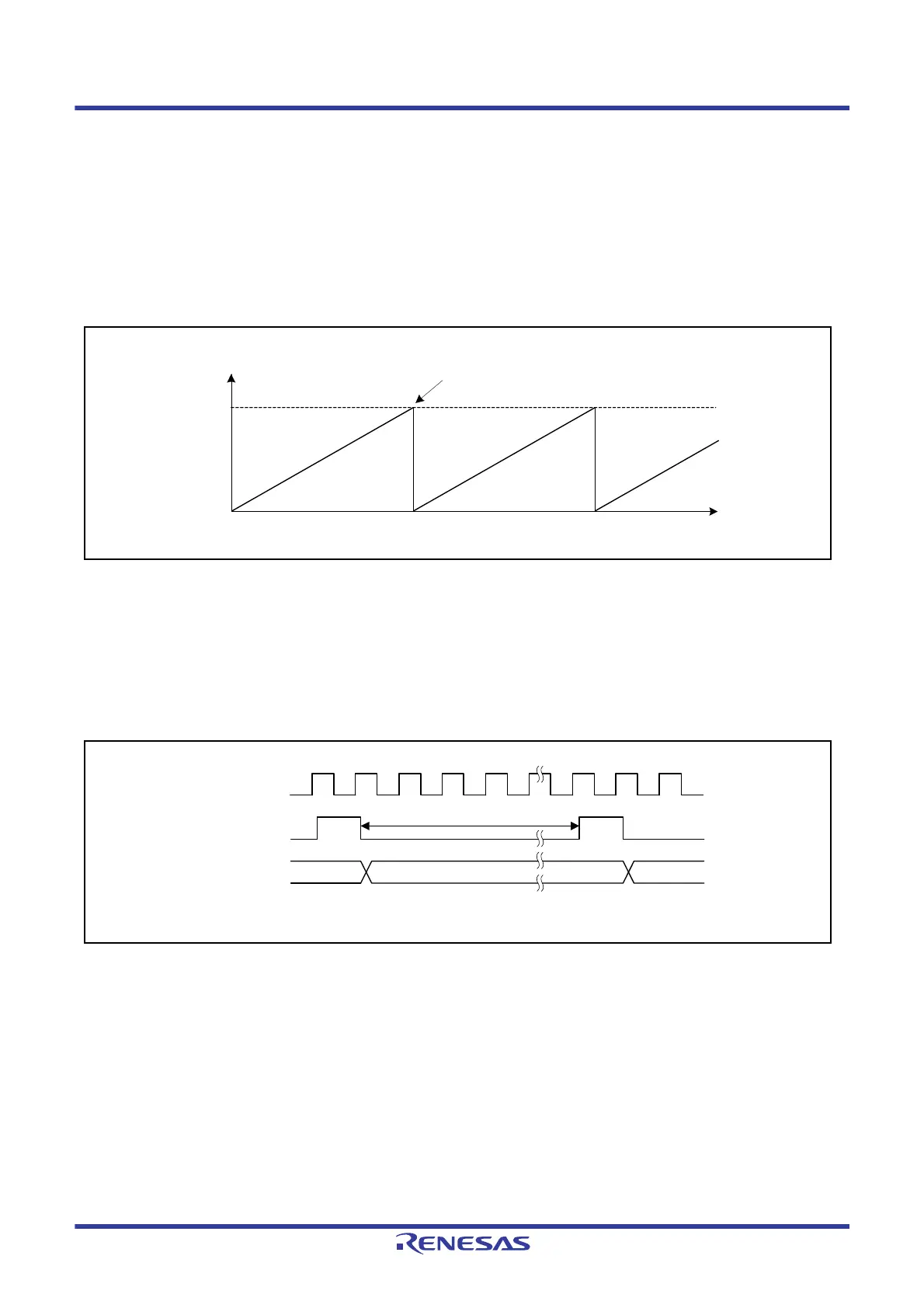

27.3.2 CMCNT Count Timing

As the count clock to be input to the CMCNT counter, one of four frequency dividing clocks (PCLK/8, PCLK/32, PCLK/

128, and PCLK/512) obtained by dividing the peripheral module clock (PCLK) can be selected with the

CMCR.CKS[1:0] bits.

Figure 27.3 shows the timing of the CMCNT counter.

Figure 27.3 CMCNT Count Timing

Time

Counter cleared by compare match with CMCOR

CMCNT value

CMCOR

0000h

PCLK

Count clock

CMCNT

N

N + 1N - 1

PCLK/ i-1 clocks

i = 8, 32, 128, or 512

Loading...

Loading...