R01UH0823EJ0100 Rev.1.00 Page 382 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

19.2.2 DTC Mode Register B (MRB)

MRB register is used to select the DTC operating mode and cannot be accessed directly from the CPU.

DTS Bit (DTC Transfer Mode Select)

The DTS bit specifies the side (transfer source or destination) to be a repeat area or block area in repeat transfer mode or

block transfer mode.

CHNS Bit (DTC Chain Transfer Select)

The CHNS bit selects the chain transfer condition.

When the CHNE bit is 0, setting of the CHNS bit is ignored. For details on the conditions to select the chain transfer,

refer to

Table 19.3, Chain Transfer Conditions.

When the next transfer is chain transfer, completion of the specified number of transfers is not determined, the interrupt

status flag for the request source is not cleared, and an interrupt request to the CPU is not generated.

CHNE Bit (DTC Chain Transfer Enable)

The CHNE bit enables or disables chain transfer.

The chain transfer condition is selected by the CHNS bit.

For details of chain transfer, refer to

section 19.4.6, Chain Transfer.

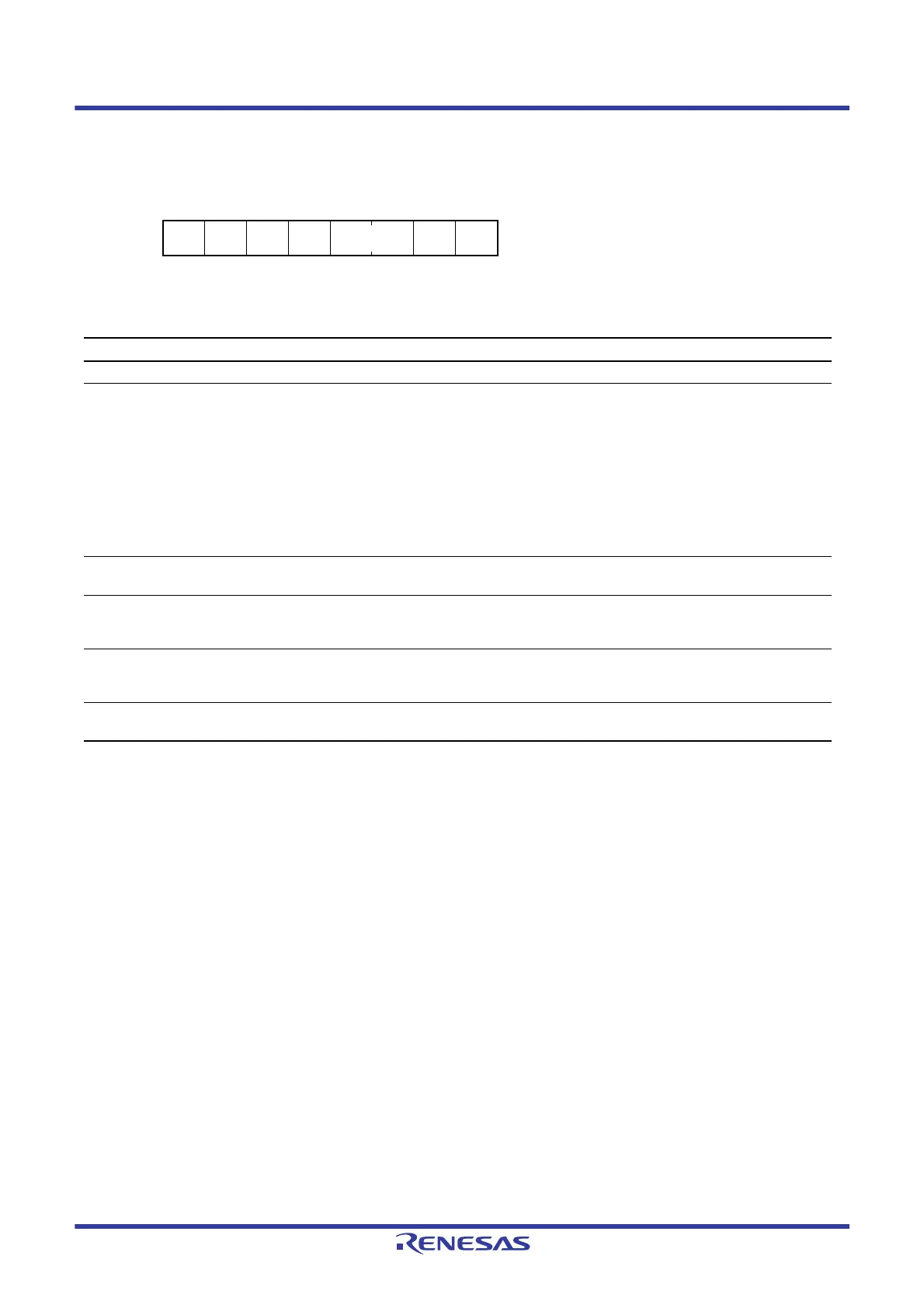

Address(es): (inaccessible directly from the CPU)

b7 b6 b5 b4 b3 b2 b1 b0

CHNE CHNS DISEL DTS DM[1:0] — —

Value after reset:

xxxxxxxx

x: Undefined

Bit Symbol Bit Name Description R/W

b1, b0 — Reserved Set these bits to 0. —

b3, b2 DM[1:0] Transfer Destination Address

Addressing Mode

b3 b2

0 0: The address in the DAR register is fixed.

(Write-back to DAR is skipped.)

0 1: The address in the DAR register is fixed.

(Write-back to DAR is skipped.)

1 0: The DAR value is incremented after data transfer.

(+1 when the MRA.SZ[1:0] bits are 00b, +2 when 01b, +4 when

10b)

1 1: The DAR value is decremented after data transfer.

(–1 when the MRA.SZ[1:0] bits are 00b, –2 when 01b, –4 when

10b)

—

b4 DTS DTC Transfer Mode Select 0: Transfer destination side is repeat area or block area.

1: Transfer source side is repeat area or block area.

—

b5 DISEL DTC Interrupt Select 0: An interrupt request to the CPU is generated on completion of the

specified number of data transfers.

1: An interrupt request to the CPU is generated for each data transfer.

—

b6 CHNS DTC Chain Transfer Select 0: Chain transfer is performed on completion of each transfer.

1: Chain transfer is performed only when the transfer counter is

changed from 1 to 0 or 1 to CRAH.

—

b7 CHNE DTC Chain Transfer Enable 0: Chain transfer is disabled.

1: Chain transfer is enabled.

—

Loading...

Loading...