TCNTS

TCDR

TCBR

TDDR

TSTR: Timer start register

TSYR: Timer synchronous register

TCR: Timer control register

NFCR: Noise filter control register

TMDR: Timer mode register

TIOR: Timer I/O control register

TIORH: Timer I/O control register H

TIORL: Timer I/O control register L

TIER: Timer interrupt enable register

TIER2: Timer interrupt enable register 2

TGCR: Timer gate control register

TOER: Timer output master enable register

TOCR1: Timer output control register 1

TOCR2: Timer output control register 2

TSR: Timer status register

TBTM: Timer buffer operation transfer mode register

TCNT: Timer counter

TCNTS: Timer subcounter

TRWER: Timer read/write enable register

TOLBR: Timer output level buffer register

TCDR: Timer cycle data register

TCBR: Timer cycle buffer register

Event signal input

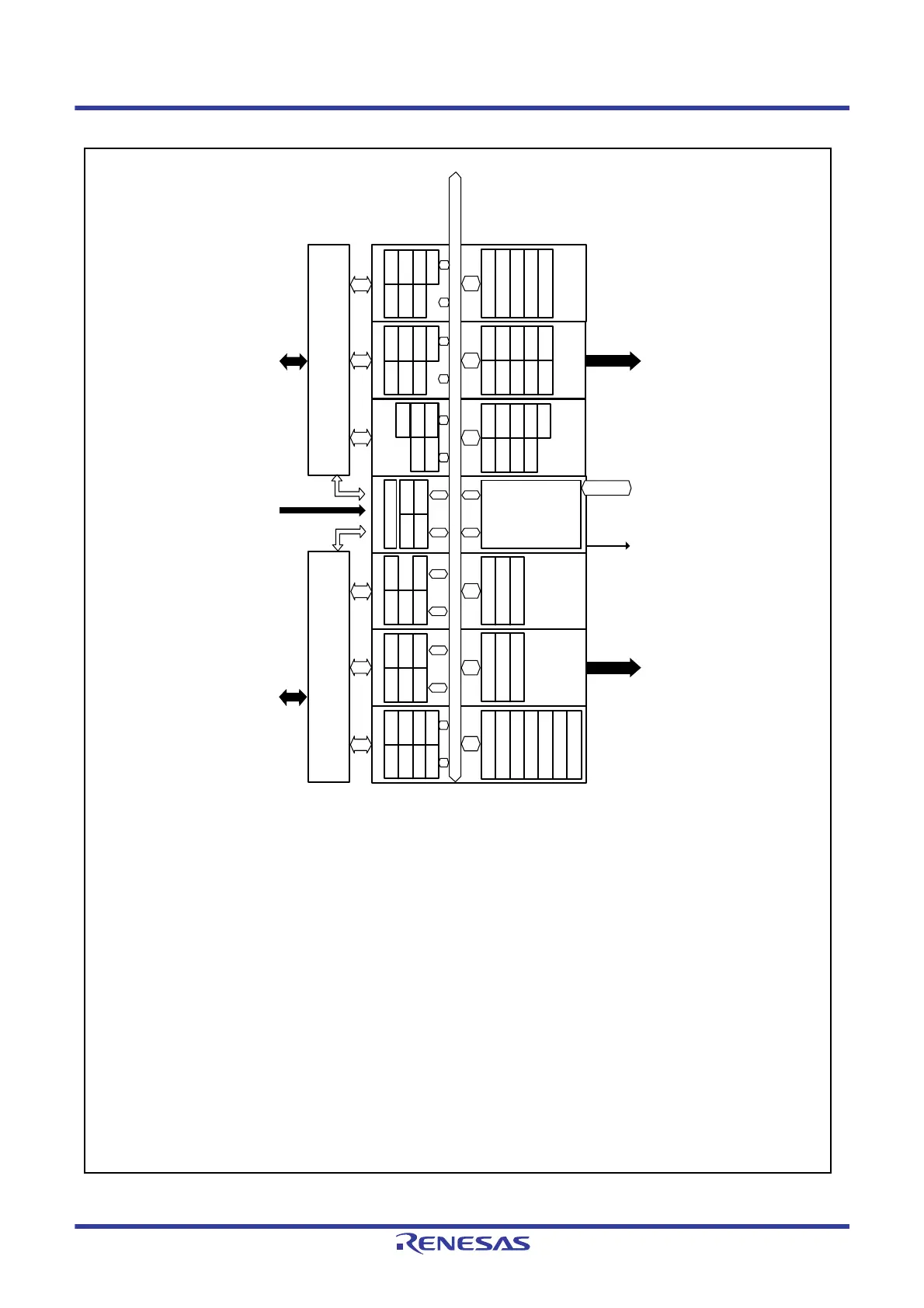

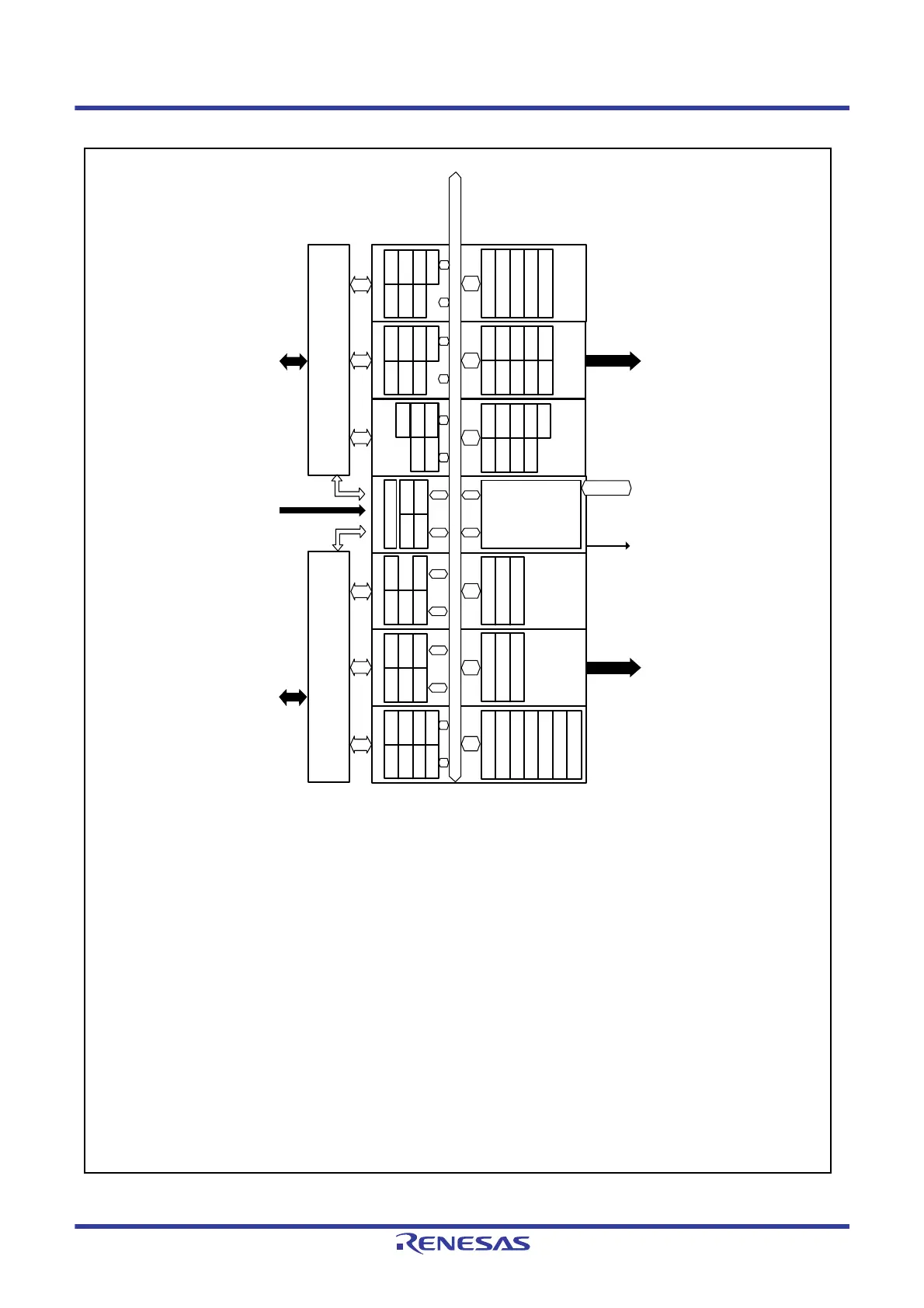

MTU1

MTU2

Event signal output

MTU1

MTU2

TCNT

TGRA

TGRB

I/O pins

MTU3: MTIOC3A

MTIOC3B

MTIOC3C

MTIOC3D

MTU4: MTIOC4A

MTIOC4B

MTIOC4C

MTIOC4D

I/O pins

Internal peripheral bus

CommonMTU0

Module data bus

Control logic for MTU3 and MTU4

MTU1 MTU2 MTU4 MTU3

TMDRTCR

TIORLTIORH

TSRTIER

TMDRTCR

TIORLTIORH

TSRTIER

TCNT

TGRA

TGRB

TGRC

TGRD

TCNT

TGRA

TGRB

TGRC

TGRD

Bus I/F

TCNT

TGRA

TGRB

TCNT

TGRA

TGRB

TGRC

TGRD

TGRE

TGRF

TMDRTCR

TIORLTIORH

TSRTIER

TCR

TIOR

TIER

TMDR

TSR

TCR

TIOR

TIER

TMDR

TSR

TSTR

TSYR

Control logic

TOER

TGCR

Control logic for MTU0 to MTU2

Clock input

Interrupt request signals

MTU3:

MTU4:

A/D converter start request signals

MTU0 to 4:

MTU0:

MTU4:

Interrupt request signals

MTU0:

MTU1:

MTU2:

NFCR

TRWER

TICCR

TBTMTIER2

TOLBR

TOCR2

TOCR1

TBTM TBTM

TWCR

TDER

TITCR

TITCNT

TBTER

TADCR

TADCORA

TADCORB

TADCOBRA

TADCOBRB

TDDR: Timer dead time data register

TGRA: Timer general register A

TGRB: Timer general register B

TGRC: Timer general register C

TGRD: Timer general register D

TGRE: Timer general register E

TGRF: Timer general register F

TICCR: Timer input capture control register

TWCR: Timer waveform control register

TADCR: Timer A/D converter start request control register

TADCORA: Timer A/D converter start request cycle set register A

TADCORB: Timer A/D converter start request cycle set register B

TADCOBRA: Timer A/D converter start request cycle set buffer register A

TADCOBRB: Timer A/D converter start request cycle set buffer register B

TITCR: Timer interrupt skipping set registers

TITCNT: Timer interrupt skipping counters register

TBTER: Timer buffer transfer set register

TDER: Timer dead time enable register

TGIA3

TGIB3

TGIC3

TGID3

TCIV3

TGIA4

TGIB4

TGIC4

TGID4

TCIV4

TRGAN

TRG0AN

TRG0BN

TRG0EN

TRG0FN

TRG4AN

TRG4BN

TRG4ABN

TGIA0

TGIB0

TGIC0

TGID0

TGIE0

TGIF0

TCIV0

TGIA1

TGIB1

TCIV1

TCIU1

TGIA2

TGIB2

TCIV2

TCIU2

MTIOC0A

MTIOC0B

MTIOC0C

MTIOC1A

MTIOC1B

MTIOC2A

MTIOC2B

MTU0:

MTU1:

MTU2:

PCLK/1

PCLK/4

PCLK/16

PCLK/64

PCLK/256

PCLK/1024

MTCLKA

MTCLKB

MTCLKC

MTCLKD

External clock:

Internal clock:

Loading...

Loading...