R01UH0823EJ0100 Rev.1.00 Page 365 of 1823

Jul 31, 2019

RX23W Group 18. DMA Controller (DMACA)

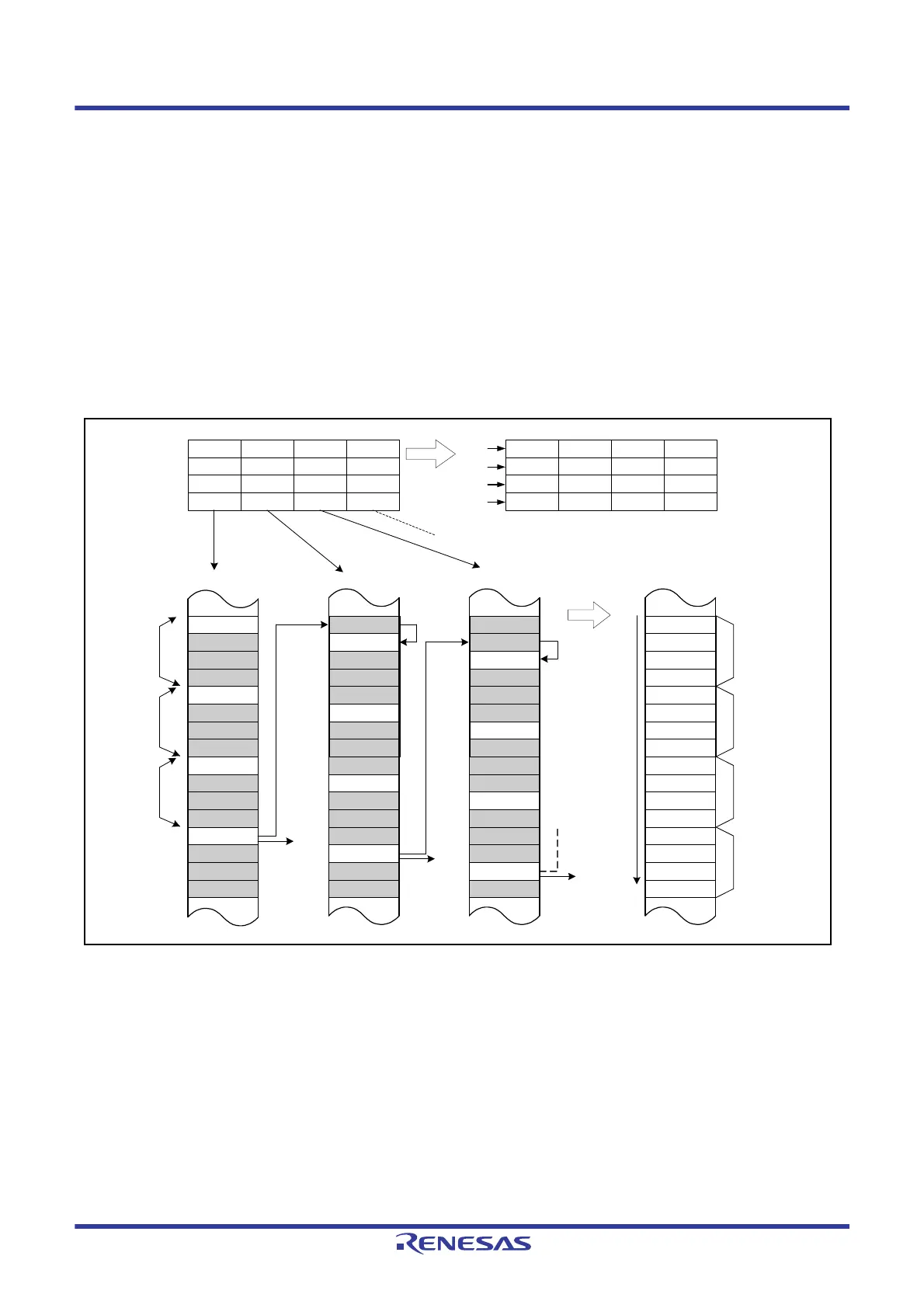

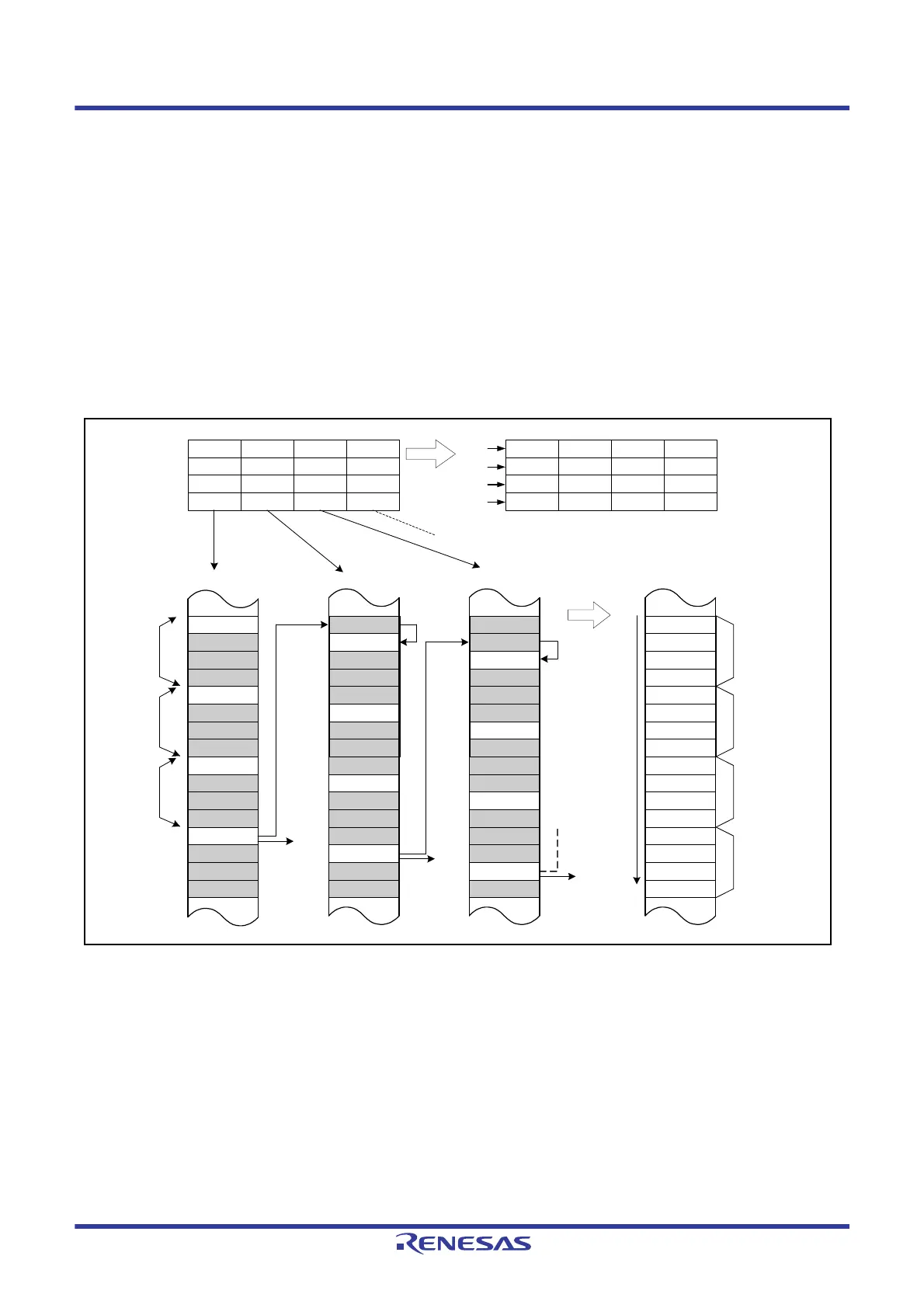

(2) Example of XY Conversion Using Offset Addition

Figure 18.8 shows the XY conversion using offset addition in repeat transfer mode.

Settings are as follows:

DMAC0.DMAMD: Transfer source address update mode: Offset addition

DMAC0.DMAMD: Transfer destination address update mode: Destination address is incremented.

DMAC0.DMTMD: Transfer data size select: 32 bits

DMAC0.DMTMD: Transfer mode select: Repeat transfer

DMAC0.DMTMD: Repeat area select: The source is specified as the repeat area.

DMAC0.DMOFR: Offset address: 10h

DMAC0.DMCRA: Repeat size: 4h

DMAC0.DMINT: The repeat size end interrupt is enabled.

Figure 18.8 XY Conversion Operation Using Offset Addition in Repeat Transfer Mode

When a transfer starts, the offset value is added to the transfer source address every time data is transferred. The transfer data

is written to the destination continuous addresses. When data 4 is transferred, which means that the repeat size of transfers is

completed, the transfer source address returns to the transfer start address (address of data 1 on the transfer source) and a

repeat size end interrupt is requested. While this interrupt stops the transfer temporarily, perform the following.

DMAC0.DMSAR: Rewrite the DMA transfer source address to the address of data 5

(with the above example, the data 1 address + 4).

DMAC0.DMCNT: Set the DTE bit to 1.

The DMA transfer is resumed from the state when the DMA transfer is stopped. After that, the operations described

above are repeated until the transfer source data is transposed to the destination area (XY conversion).

Transfer

Data 1

Data 5

Data 9

Data 13

Data 2

Data 6

Data 10

Data 14

Data 3

Data 7

Data 11

Data 15

Data 4

Data 8

Data 12

Data 16

Data 1

Data 5

Data 9

Data 13

Data 2

Data 6

Data 10

Data 14

Data 3

Data 7

Data 11

Data 15

Data 4

Data 8

Data 12

Data 16

Data 1

Data 5

Data 9

Data 13

Data 2

Data 6

Data 10

Data 14

Data 3

Data 7

Data 11

Data 15

Data 4

Data 8

Data 12

Data 16

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

Data 8

Data 9

Data 10

Data 11

Data 12

Data 13

Data 14

Data 15

Data 16

set va

ue

set va

ue

set va

ue

Address

returned

Transfer source

address written by

CPU

Interrupt

request

generated

Transfer source

address written by

CPU

Address

returned

Interrupt

request

generated

Interrupt

request

generated

First

cycle

Second

cycle

Third

cycle

Fourth

cycle

Data 1

Data 2

Data 3

Data 4

Data 5

Data 6

Data 7

Data 8

Data 9

Data 10

Data 11

Data 12

Data 13

Data 14

Data 15

Data 16

Data 1 Data 2 Data 3 Data 4

Data 5 Data 6 Data 7 Data 8

Data 9 Data 10 Data 11 Data 12

Data 13 Data 14 Data 15 Data 16

Transfer

First

cycle

Second cycle

Third cycle

Fourth cycle

First cycle Second cycle Third cycle

Loading...

Loading...