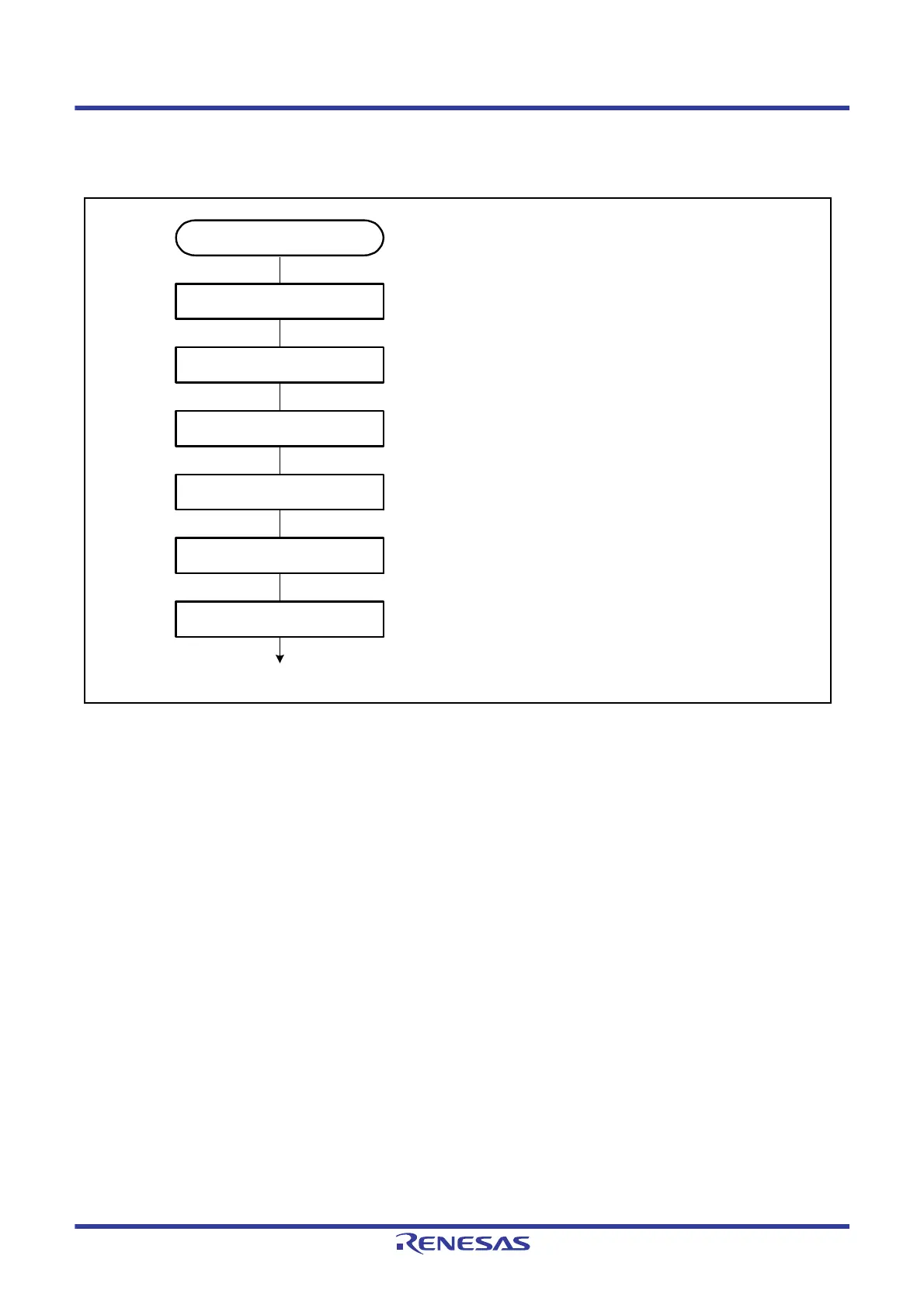

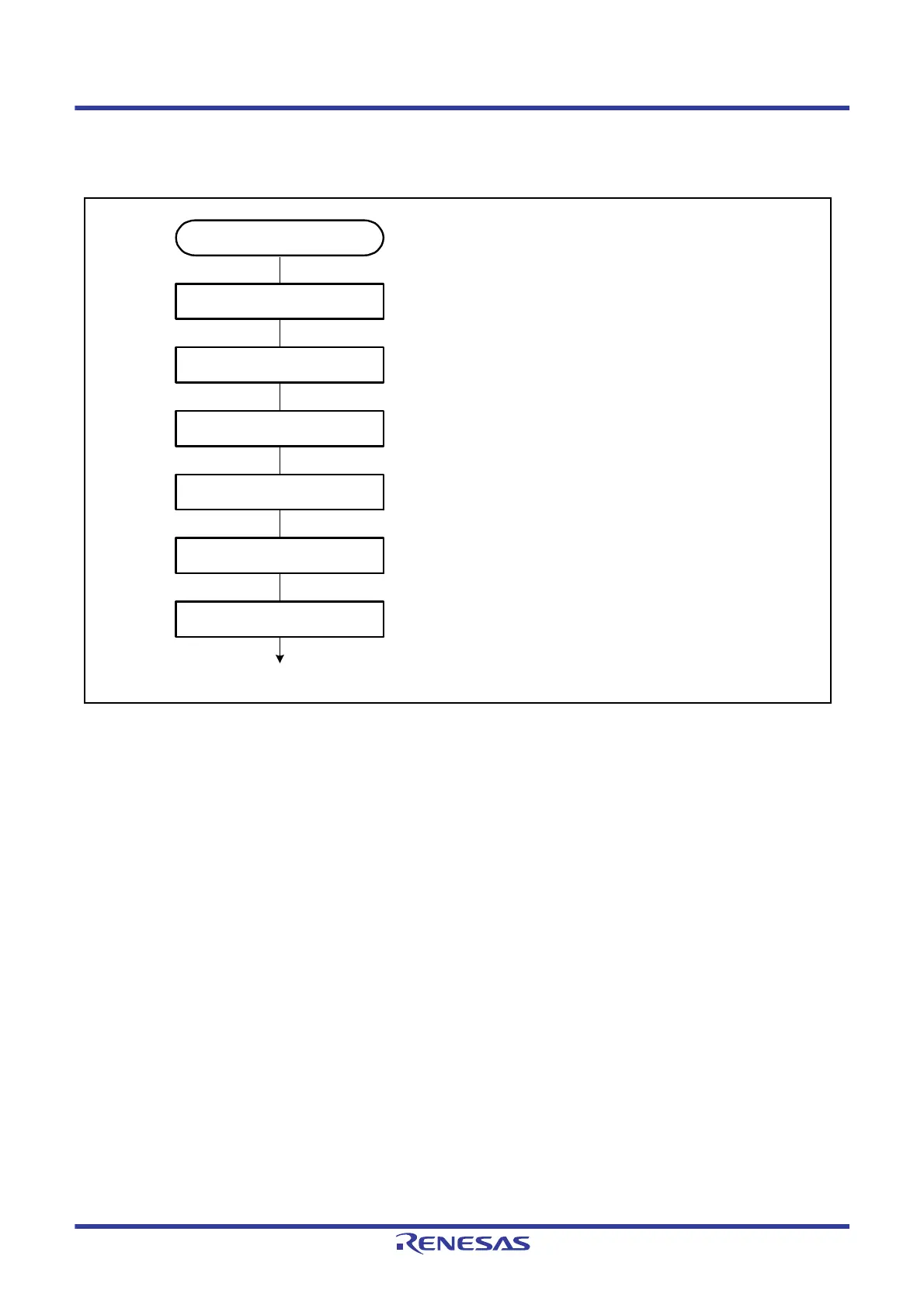

[1] Select the count clock with the TPSC[2:0] bits in

TCR. At the same time, select the input clock

edge with the CKEG[1:0] bits in TCR.

[2] Select the TGRy register to be used as the

TCNT clearing source with the CCLR[2:0] bits in

TCR (y = A to D).

[3] Set TGRy as an output compare register by

TIOR, and select the initial value and output

value.

[4] Set the cycle in TGRy selected in [2], and set the

duty in the other TGRy registers.

[5] Select the PWM mode with the MD[3:0] bits in

TMDR.

[6] Set the TPU.TSTR.CSTj bit (j = 0 to 5) to 1 to

start the counter operation.

Loading...

Loading...