R01UH0823EJ0100 Rev.1.00 Page 727 of 1823

Jul 31, 2019

RX23W Group 26. 8-Bit Timer (TMR)

: Possible

—: Impossible

Note 1. For details, refer to section 33, Serial Communications Interface (SCIg, SCIh).

Note 2. For details, refer to section 11, Low Power Consumption.

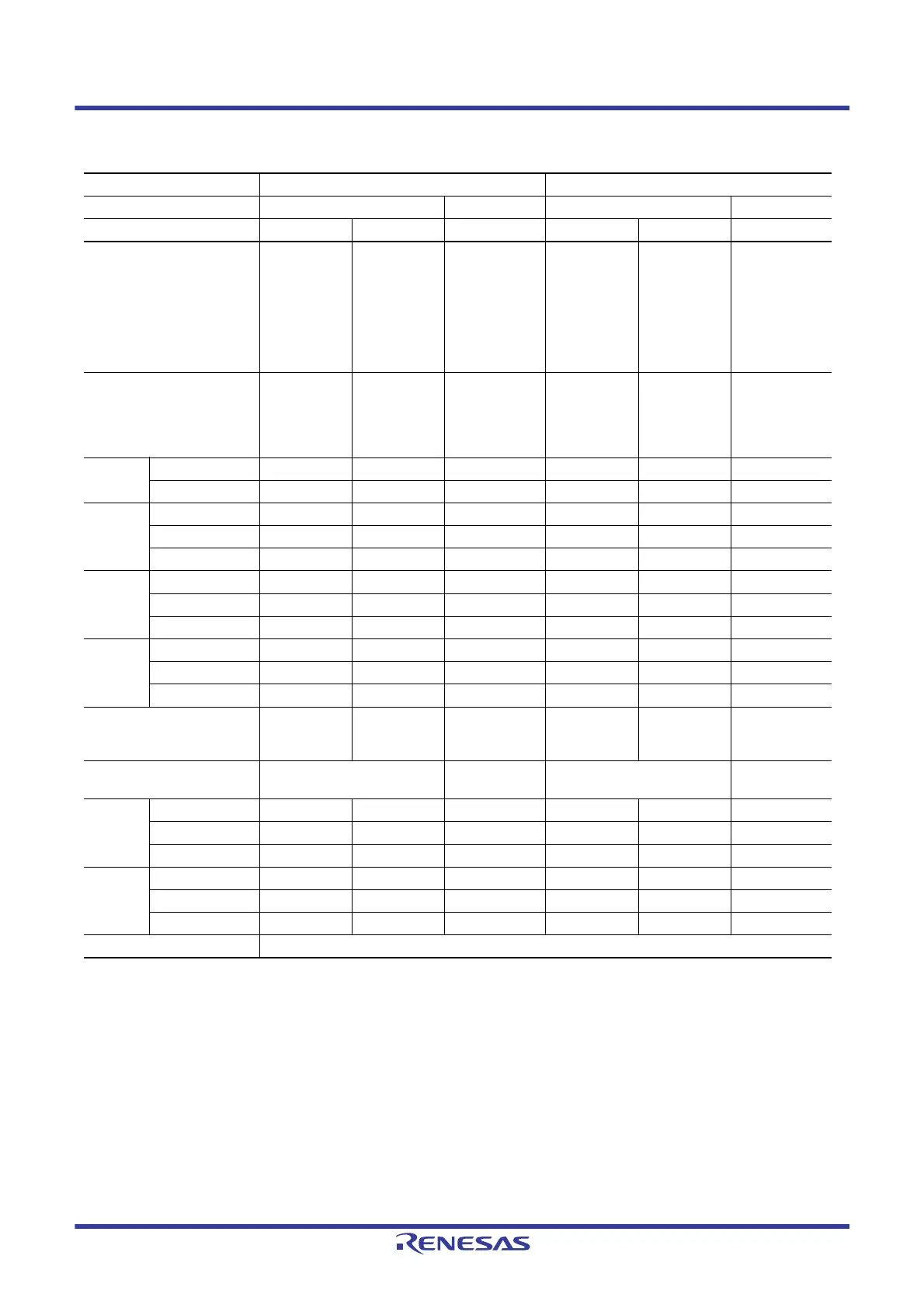

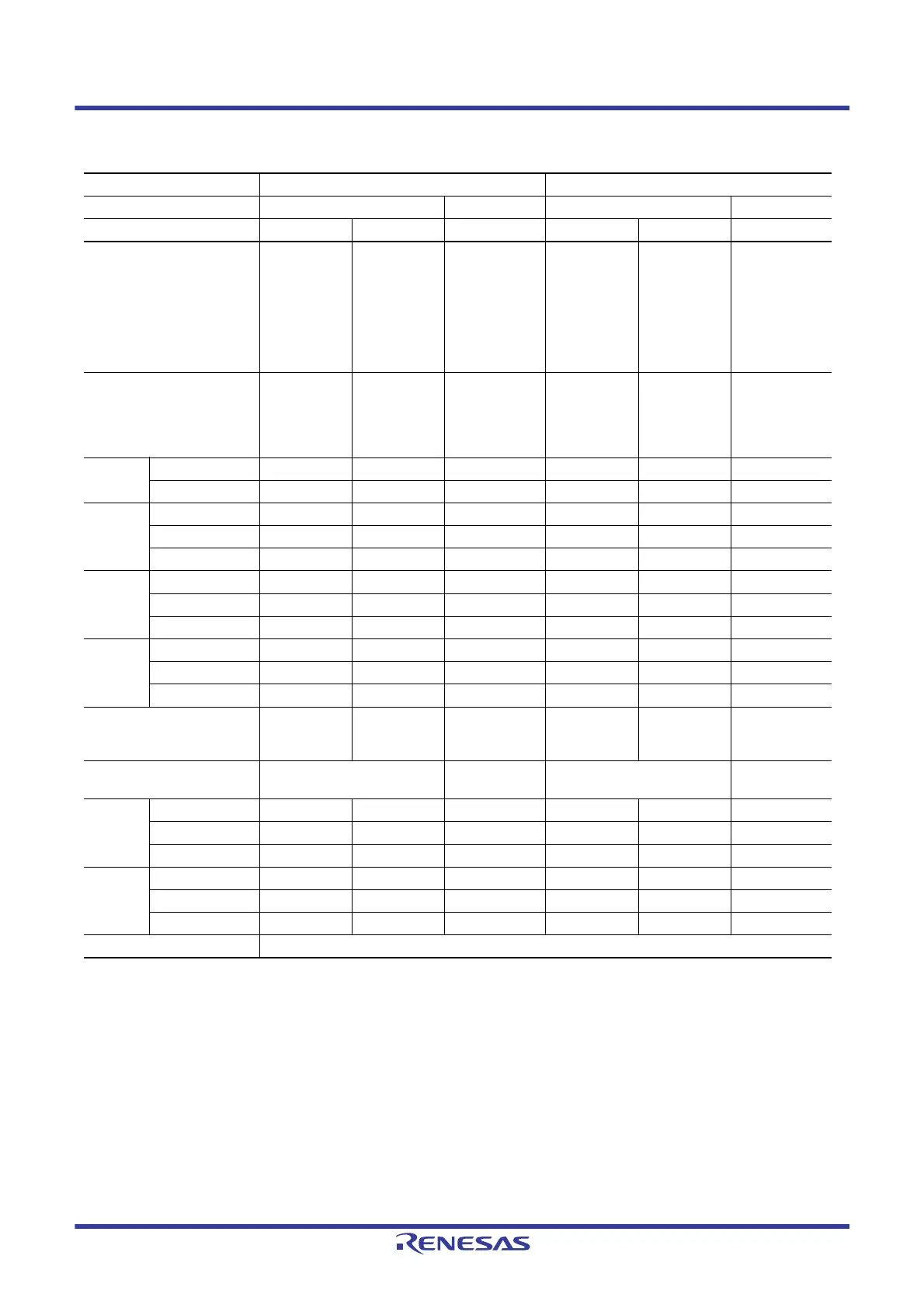

Table 26.2 TMR Functions

Item Unit 0 Unit 1

Counter mode 8 Bits 16 Bits 8 Bits 16 Bits

Channel TMR0 TMR1 TMR0 + TMR1 TMR2 TMR3 TMR2 + TMR3

Count clock PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI0

PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI1

PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI1

PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI2

PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI3

PCLK/1

PCLK/2

PCLK/8

PCLK/32

PCLK/64

PCLK/1024

PCLK/8192

TMCI3

Counter clear TMR0.TCORA

TMR0.TCORB

TMR1.TCORA

TMR1.TCORB

TMRI1

TMR0.TCORA +

TMR1.TCORA

TMR0.TCORB +

TMR1.TCORB

TMR2.TCORA

TMR2.TCORB

TMRI2

TMR3.TCORA

TMR3.TCORB

TMRI3

TMR2.TCORA +

TMR3.TCORA

TMR2.TCORB +

TMR3.TCORB

TMRI2

Compare

match

Compare match A

Compare match B

Timer

output

Low output —

High output —

Toggle output —

DTC

activation

Compare match A

Compare match B

TCNT overflow — — — — — —

Interrupt Compare match A CMIA0 CMIA1 CMIA0 CMIA2 CMIA3 CMIA2

Compare match B CMIB0 CMIB1 CMIB0 CMIB2 CMIB3 CMIB2

TCNT overflow OVI0 OVI1 OVI0 OVI2 OVI3 OVI2

Cascaded connection TMR1 overflow TMR0

compare

match A

— TMR3 overflow TMR2

compare

match A

—

SCI baud rate clock

generation*

1

———

ELC

output

event

Compare match A

— —

Compare match B — —

TCNT overflow — —

ELC input

event

Counting start —— ——

Event counting

—— ——

Counting restart

—— ——

Module stop setting*

2

MSTPCRA.MSTPA5 bit (unit 0), MSTPCRA.MSTPA4 bit (unit 1)

Loading...

Loading...