374 Chapter7

ADC/Interface Section

A3 Assembly Video Circuits

SWEEP CONT SGL or PRESET.

Video Filter Buffer Amplifier

Refer to function block W of A3 Interface Assembly Schematic

Diagram (sheet 5 of 6) in the

HP 8560 E-Series Spectrum Analyzer

Component Level Information.

The video filter buffer amplifier provides outputs for video trigger,

positive and negative peak detectors, and the analog zero-span (sweeps

<30 ms). The zero-span video output is terminated in 500 ohms on the

A2 Controller assembly. The amplifier is a high-input-impedance buffer

amplifier with a gain of one when properly terminated.

Current source U307C provides twice the current of Q316. Resistor

R145 and current source U307D shift the dc level. Resistor R260

terminates the peak detector inputs in 500 ohms. The unterminated

gain is 1.1. Diode CR114 prevents latchup during positive overdrive

conditions while CR113 protects Q318 during overdrive. Diode CR117

is a 12.7 V zener that limits the peak detector output to +1.5 V.

Typically, limiting occurs at +1.1 V.

Positive/Negative Peak Detectors

Refer to function blocks Y and Z of A3 Interface Assembly Schematic

Diagram (sheet 5 of 6) in the

HP 8560 E-Series Spectrum Analyzer

Component Level Information.

The following information pertains to the positive peak detector and is

applicable to troubleshooting the negative peak detector.

The positive peak detector consists of an input amplifier (A3U204 and

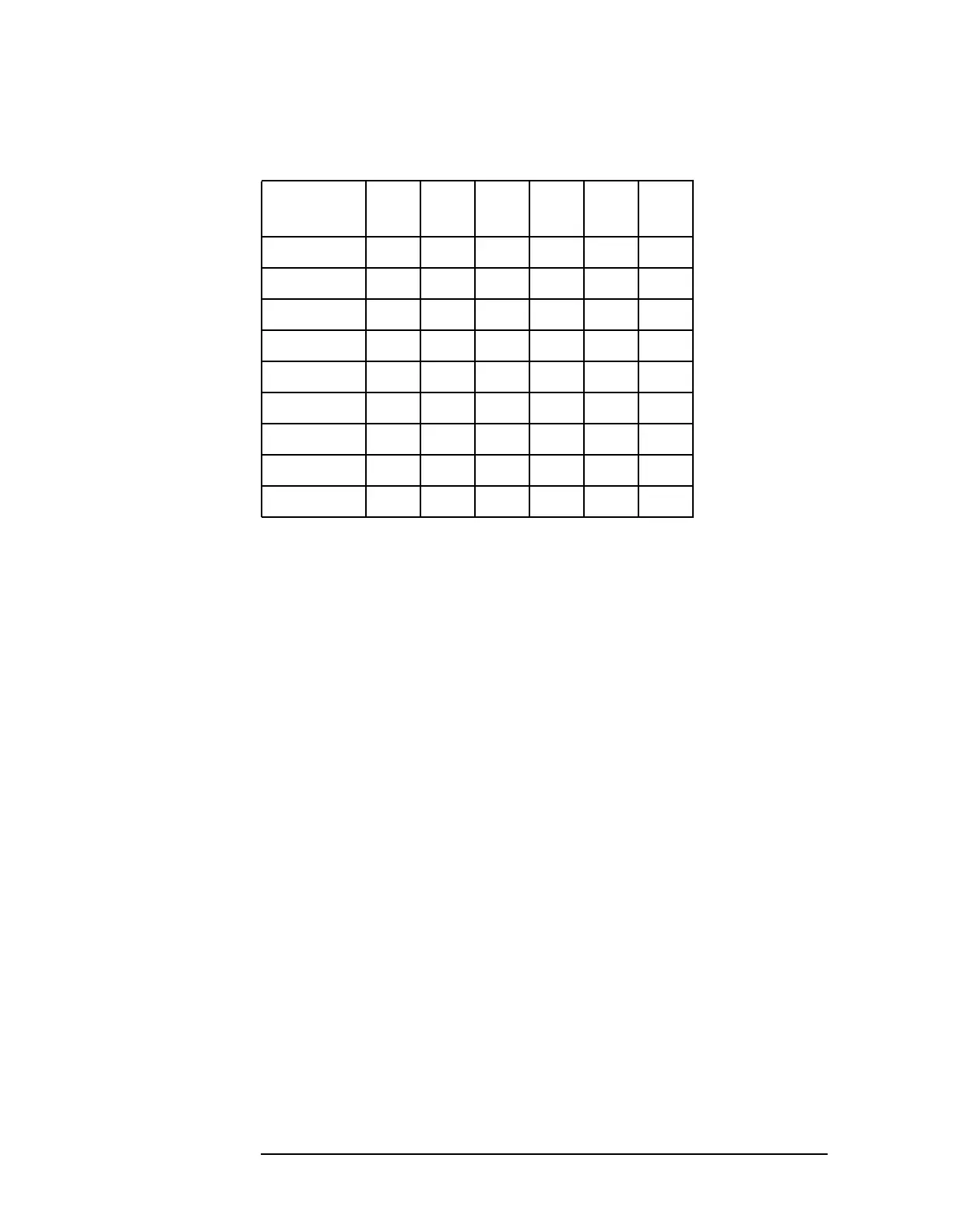

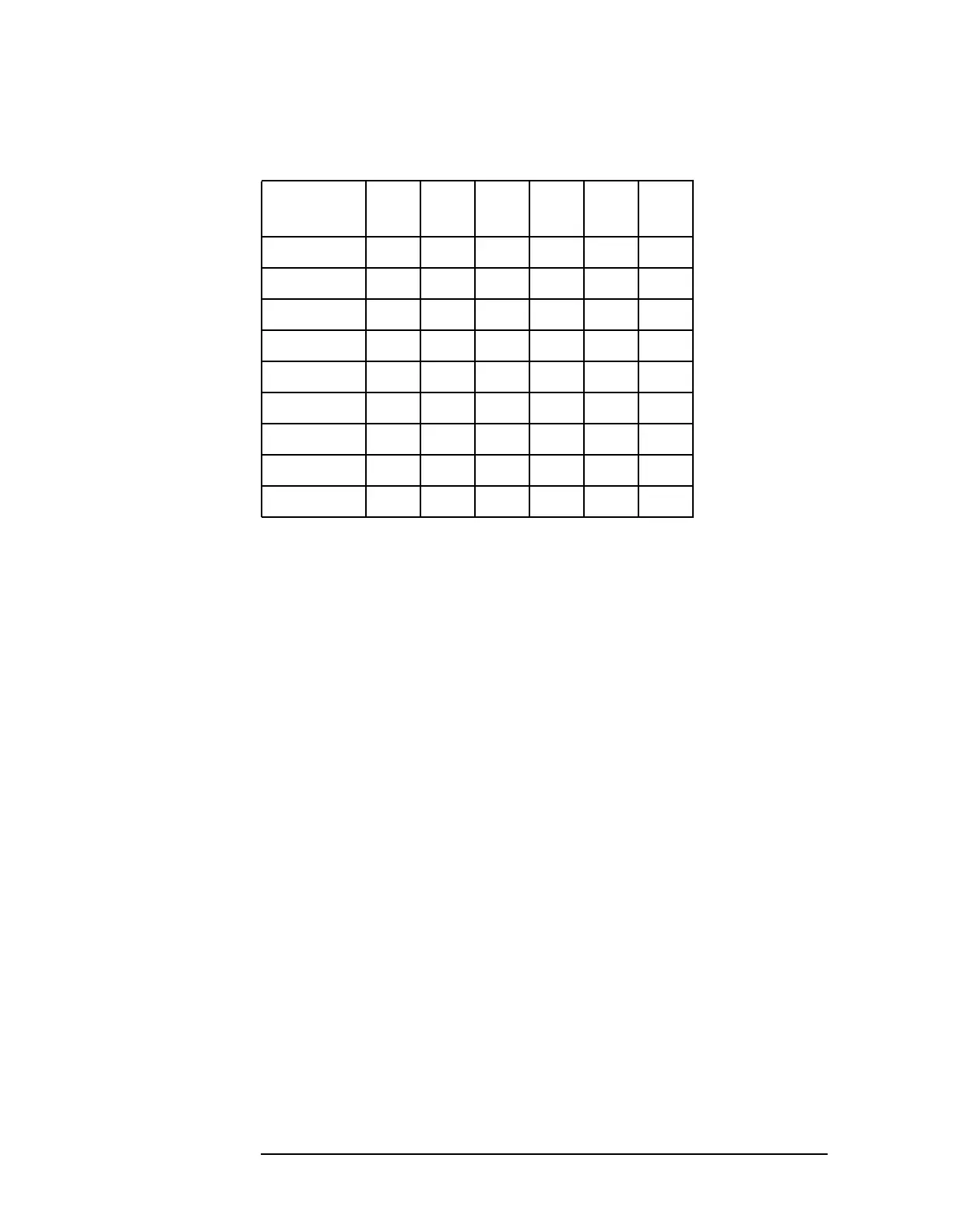

Table 7-7 A3U102 Latch Outputs

Video BW Pin

2

Pin

5

Pin

7

Pin

10

Pin

12

Pin

15

300 Hz H LLLLL

1 kHz LLLLLH

3 kHz LHLLLL

10 kHz LLLLHL

30 kHz H L H L L L

100 kHz L L H L L H

300 kHz L H H L L L

1 MHz L L H L H L

3 MHz LLLHLL

Loading...

Loading...