Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 105

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

AXI4-Lite Slave Control/Status Register Map Detailed Descriptions

ECC_STATUS

This register holds information on the occurrence of correctable and uncorrectable errors.

The status bits are independently set to 1 for the first occurrence of each error type. The

status bits are cleared by writing a 1 to the corresponding bit position; that is, the status bits

can only be cleared to 0 and not set to 1 using a register write. The ECC Status register

operates independently of the ECC Enable Interrupt register.

ECC_EN_IRQ

This register determines if the values of the CE_STATUS and UE_STATUS bits in the ECC

Status Register assert the Interrupt output signal (ECC_Interrupt). If both CE_EN_IRQ and

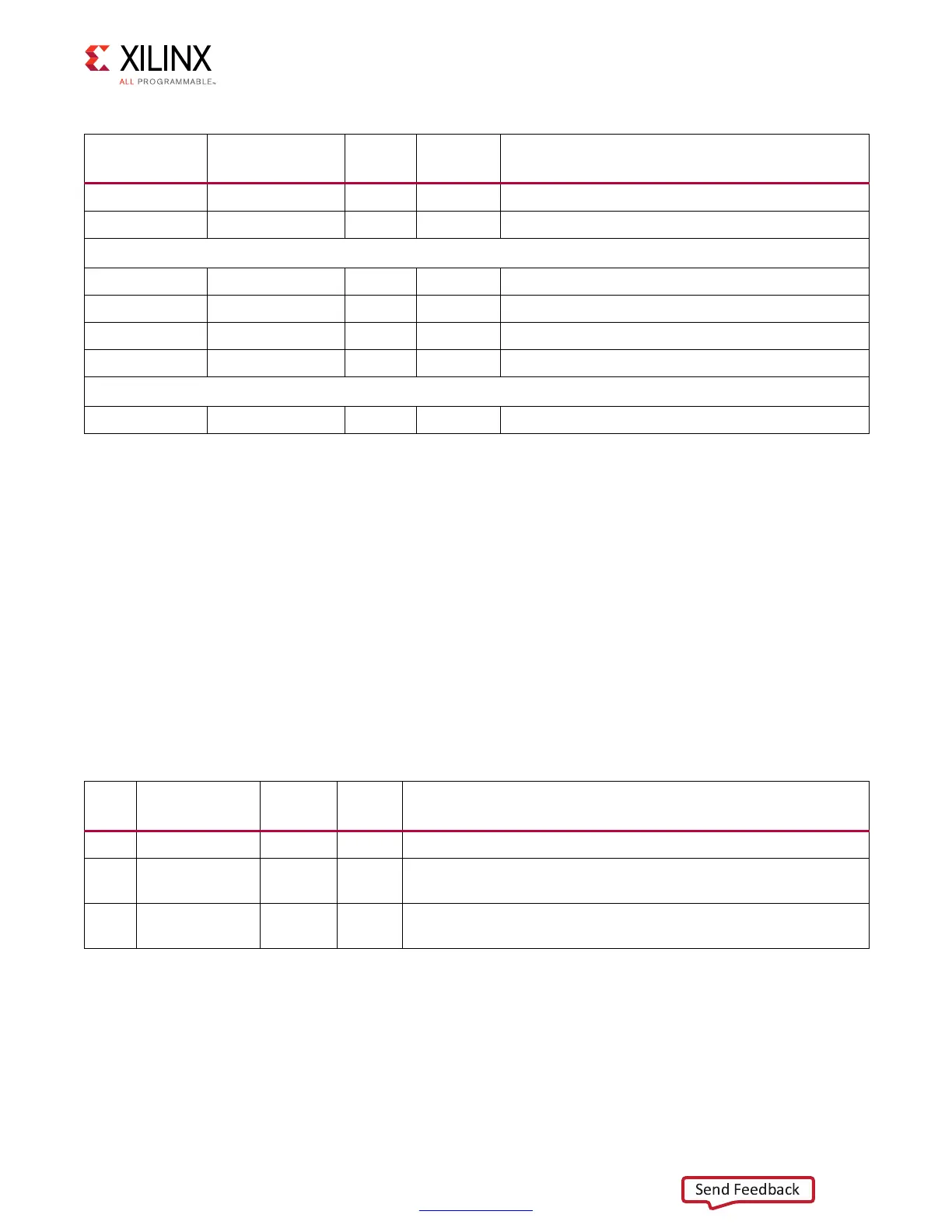

0x2C0 UE_FFA[31:0] R 0x0 Uncorrectable Error First Failing Address

0x2C4 UE_FFA[63:32]

(2)

R 0x0 Uncorrectable Error First Failing Address

(0x2C8–0x2FC) Reserved

0x300 FI_D[31:0]

(3)

W 0x0 Fault Inject Data Register

0x304 FI_D[63:32]

(3)

W 0x0 Fault Inject Data Register

0x308 FI_D[95:64]

(1)(3)

W 0x0 Fault Inject Data Register

0x30C FI_D[127:96]

(1)(3)

W 0x0 Fault Inject Data Register

(0x340–0x37C) Reserved

0x380 FI_ECC

(3)

W 0x0 Fault Inject ECC Register

Notes:

1. Data bits 64–127 are only enabled if the DQ width is 144 bits.

2. Reporting address bits 63–32 are only available if the address map is > 32 bits.

3. FI_D* and FI_ECC* are only enabled if ECC_TEST parameter has been set to 1.

Table 1-23: ECC Control Register Map (Cont’d)

Address Offset Register Name

Access

Type

Default

Value

Description

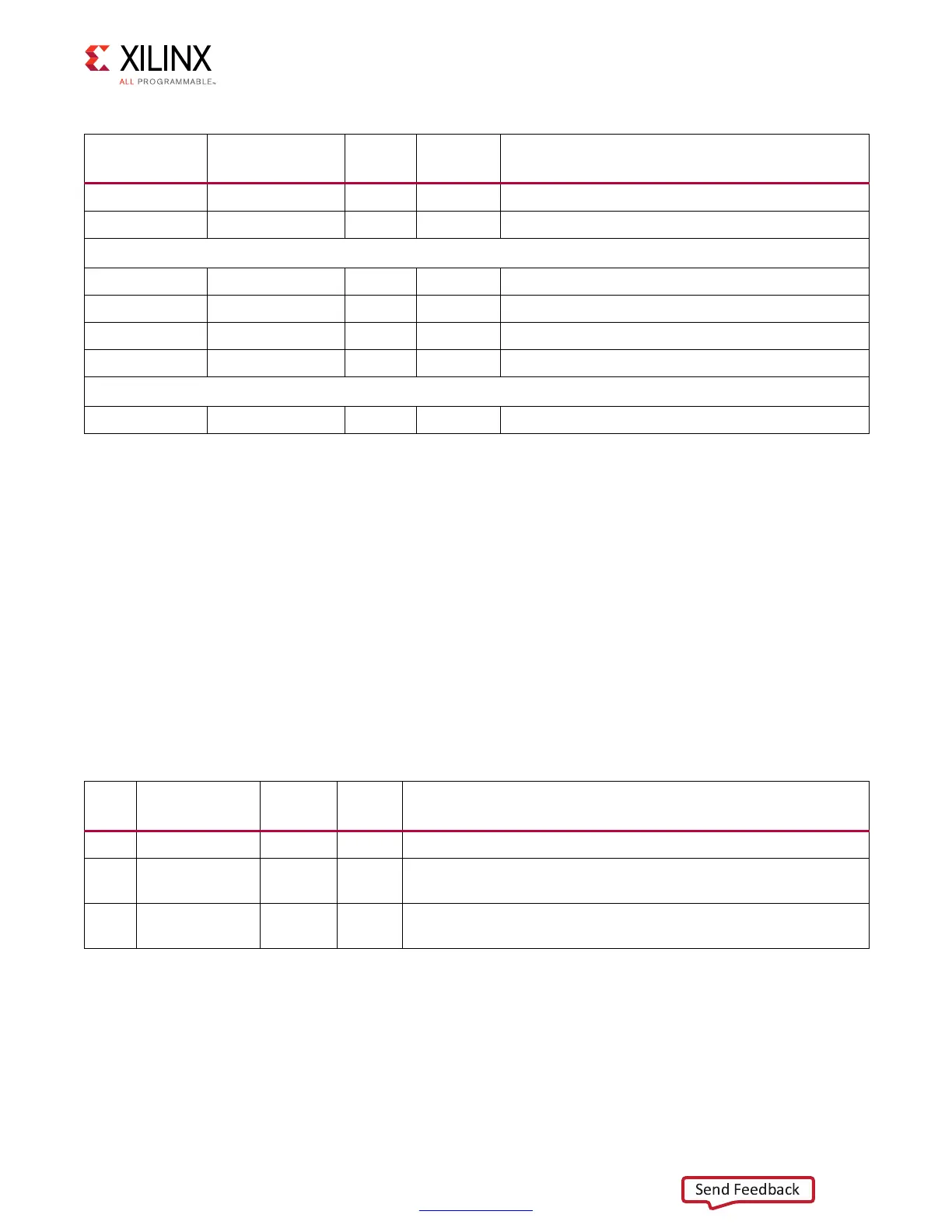

Table 1-24: ECC Status Register Bit Definitions

Bits Name

Core

Access

Reset

Value

Description

31:2 Reserved RSVD – Reserved

1 CE_STATUS R/W 0

If 1, a correctable error has occurred. This bit is cleared when a 1

is written to this bit position.

0 UE_STATUS R/W 0

If 1, an uncorrectable error has occurred. This bit is cleared when

a 1 is written to this bit position

Loading...

Loading...