Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 509

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

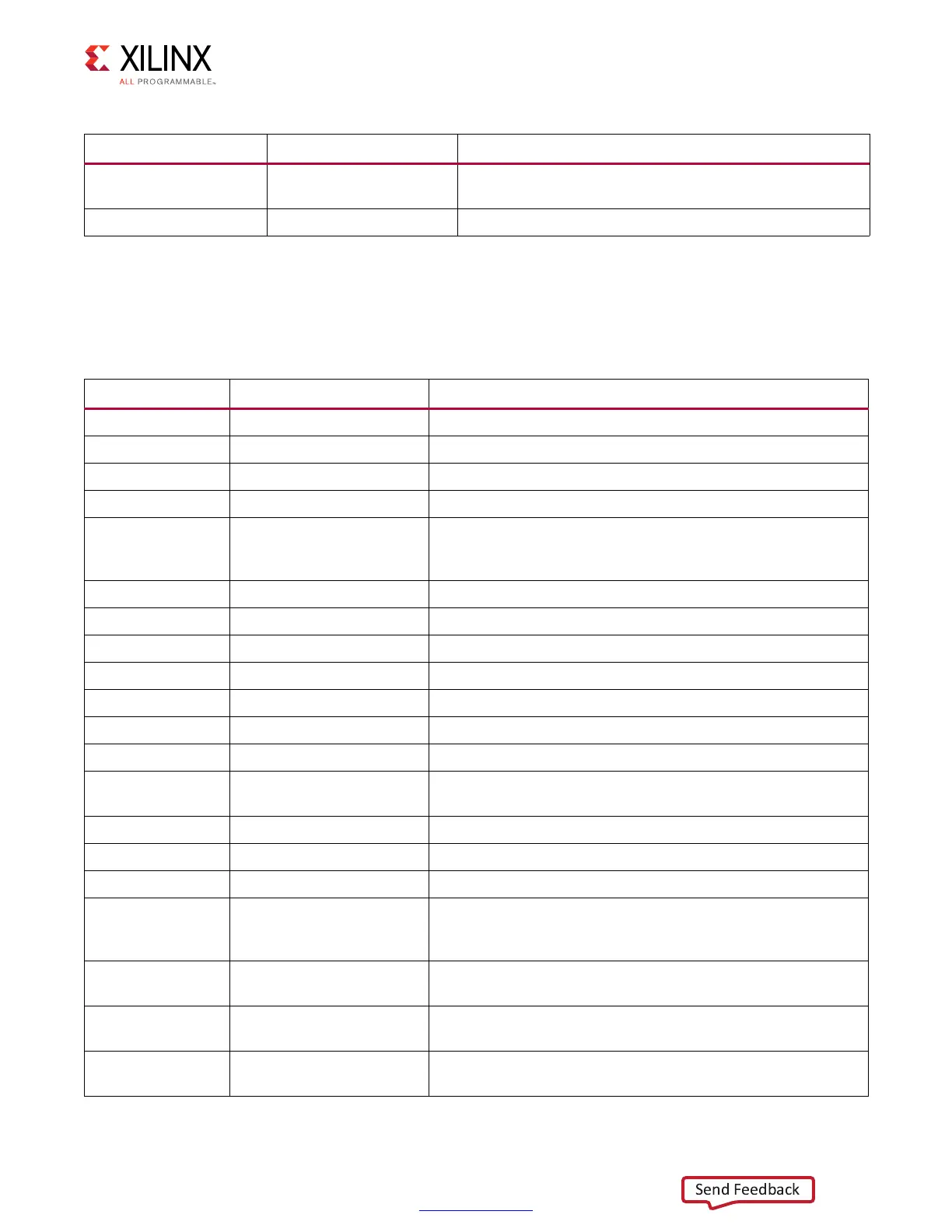

Write Calibration Debug Map

Table 3-32 indicates the mapping between bits within the dbg_wr_cal bus and debug

signals in the PHY.

dbg_stage2_cal[38] error_adj_latency

Indicates error when target PHY_LATENCY cannot be

achieved

dbg_stage2_cal[127:39] Reserved Reserved

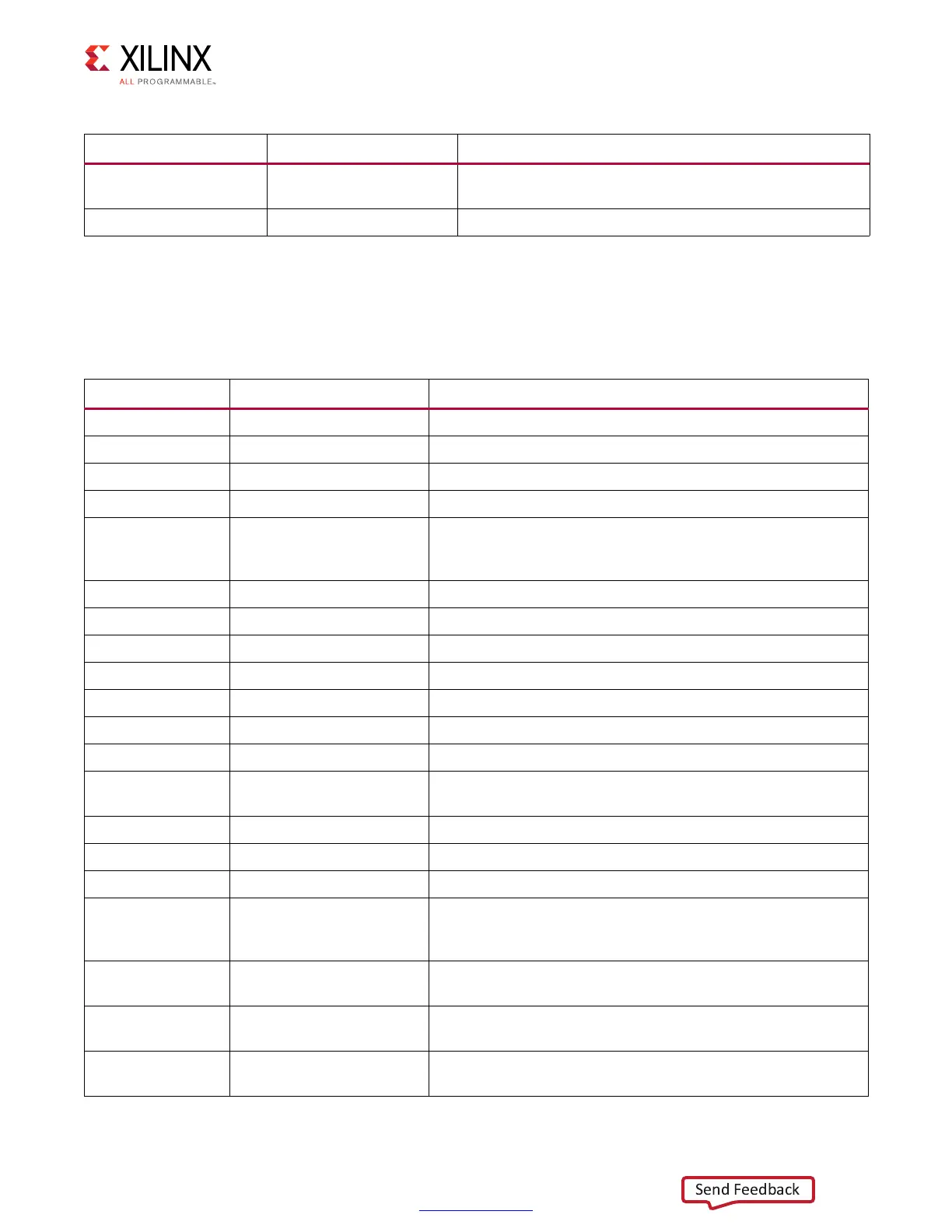

Table 3-31: Read Stage 2 Debug Signal Map (Cont’d)

Bits PHY Signal Name Description

Table 3-32: Write Debug Signal Map

Bits PHY Signal Name Description

dbg_wrcal[3:0] write_cal_cs State machine current state register

dbg_wrcal[4] data_valid_r Data is valid across data_valid_cnt FPGA logic clock cycles

dbg_wrcal[5] first_edge_found Flag to indicate first edge is found

dbg_wrcal[6] second_edge_found Flag to indicate second edge is found

dbg_wrcal[7] rdlvl_timeout_error

Flag to indicate timeout error to ensure enough time given to

stage 2 edge advanced calibration so you can sample the

results of a given byte lane.

dbg_wrcal[8] inc_byte_lane_cnt Flag to increment byte lane counter

dbg_wrcal[14:9] po_fine_taps PHASER_OUT current tap setting

dbg_wrcal[20:15] po_fine_first_edge PHASER_OUT first edge tap

dbg_wrcal[26:21] po_fine_second_edge PHASER_OUT second edge tap

dbg_wrcal[27] stg2_eod PHASER_OUT stage 2 end of delay

dbg_wrcal[28] stg3_eod PHASER_OUT stage 3 end of delay

dbg_wrcal[37:29] po_counter_read_val PHASER_OUT counter value from the PHY

dbg_wrcal[40:38] wrcal_stg

Flag to indicate which stage of write calibration is currently

running

dbg_wrcal[41] record_po_taps Flag to record a given PHASER_OUT value

dbg_wrcal[42] data_valid Instantaneous data valid check for a given byte lane

dbg_wrcal[48:43] wrcal_byte_sel Byte lane counter

dbg_wrcal[49] window_valid

When first edge and second edge are found, a check is done

to ensure the window is larger than a set size. If too small and

first/second edges cleared, this bit keeps going.

dbg_wrcal[54:50] data_valid_cnt

Counter used to check multiple read samples to ensure data is

valid

dbg_wrcal[60:55] po_fine_prev_taps

“Previous” counter to record direction so you know which

direction to move to when an edge found.

dbg_wrcal[61] first_edge_eod

First edge not a true edge, hit the limit of the PHASER_OUT

taps

Loading...

Loading...