Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 294

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

Extended FPGA Options

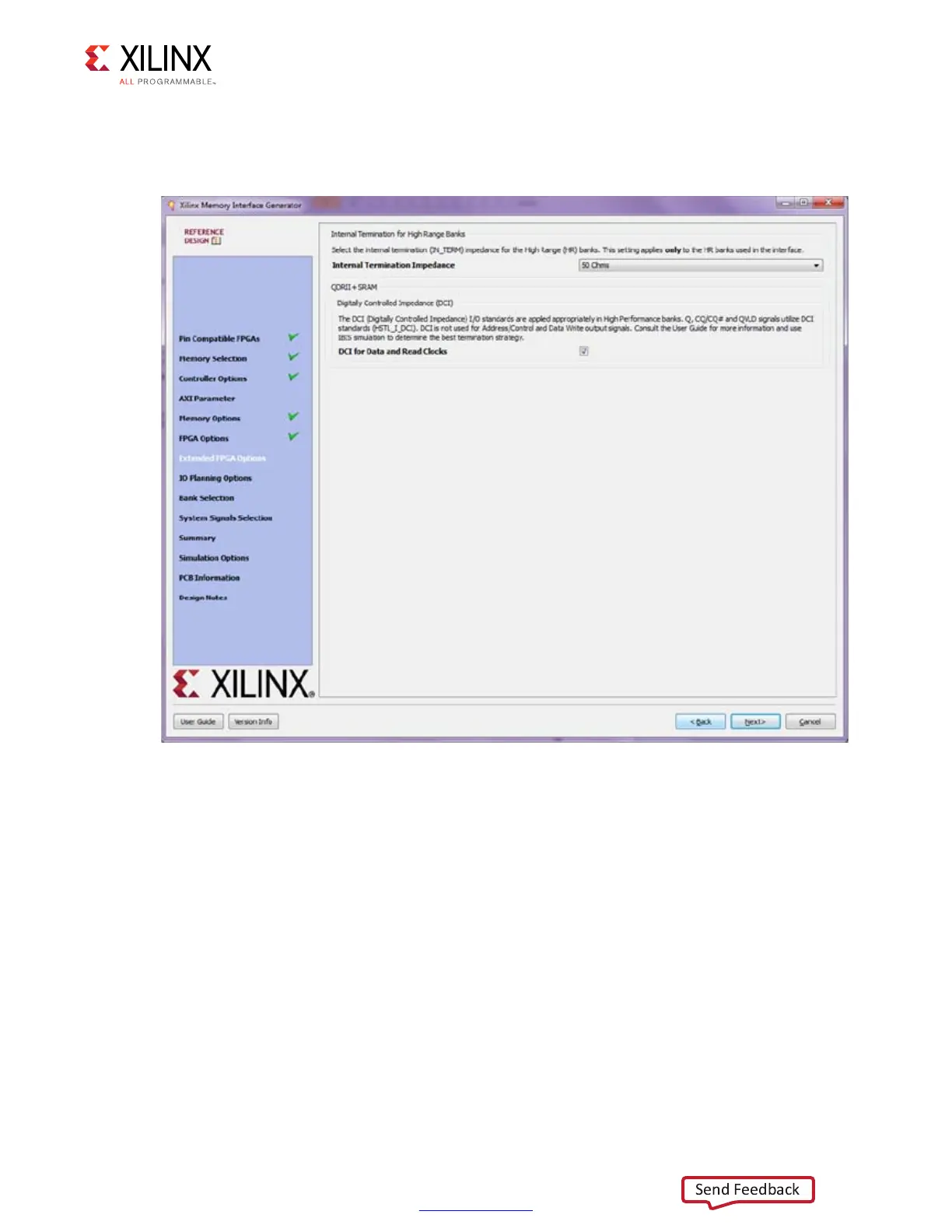

Figure 2-22 shows the Extended FPGA Options page.

• Digitally Controlled Impedance (DCI) – When selected, this option internally

terminates the signals from the QDR II+ SRAM read path. DCI is available in the High

Performance Banks.

• Internal Termination for High Range Banks – The internal termination option can be

set to 40, 50, or 60Ω or disabled. This termination is for the read datapath from the

QDR II+ SRAM. This selection is only for High Range banks.

X-Ref Target - Figure 2-22

Figure 2-22: Extended FPGA Options Page

Loading...

Loading...