Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 492

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

Memory Initialization

For simulation, the MIG tool sets up the design parameters such that long wait times usually

required for memory initialization are skipped. These parameters can result in memory

model warnings. For the design to properly initialize and calibrate the full memory array in

hardware, the top-level MIG tool design file (example_top.v) cannot use any abbreviated

value for these parameters. The MIG tool output properly sets the abbreviated values in the

test bench and the full range values in the top-level design module.

Calibration

Calibration completes read leveling and read enable calibration. This is completed over

three stages. This sequence successfully completes when the init_calib_complete

signal is asserted. For more details, see Physical Interface, page 436.

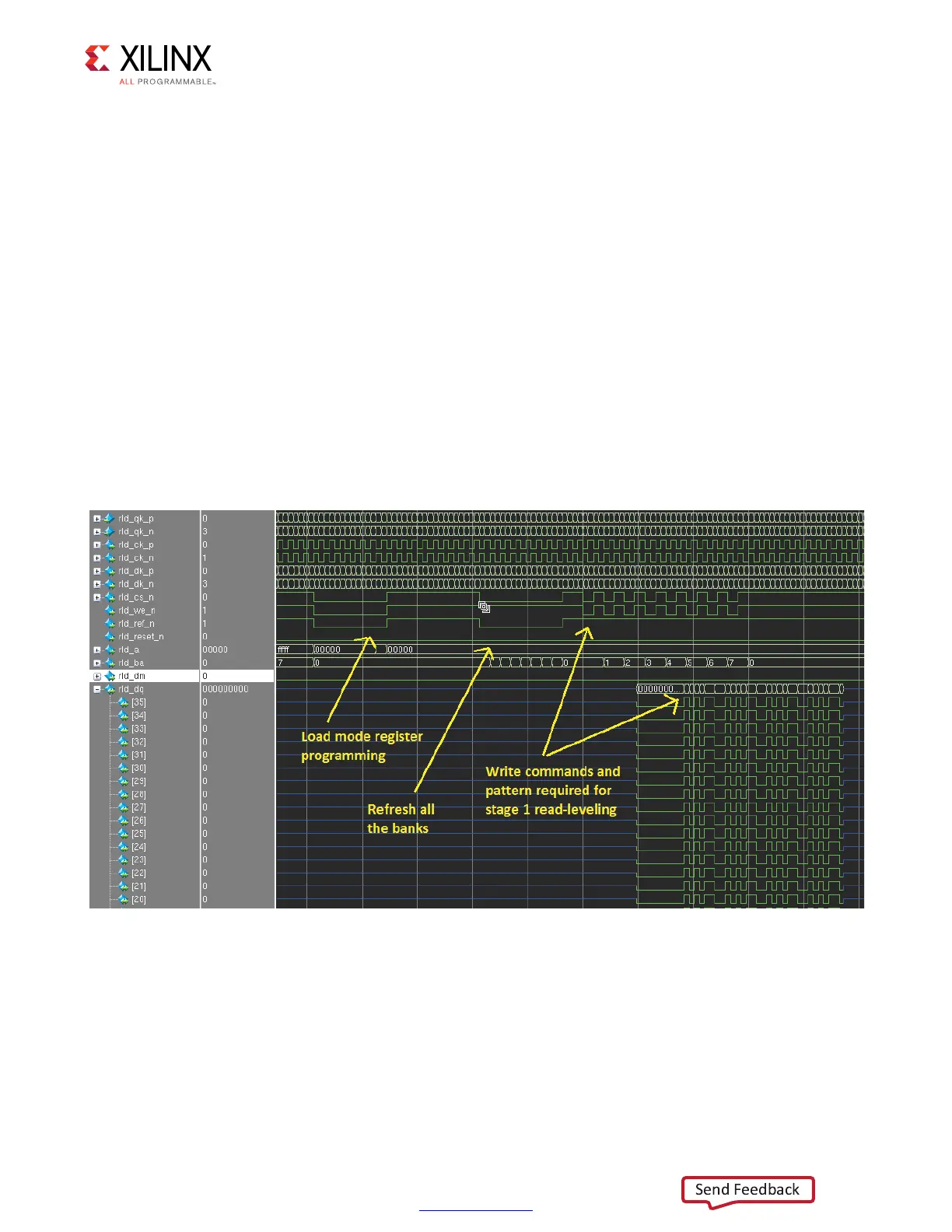

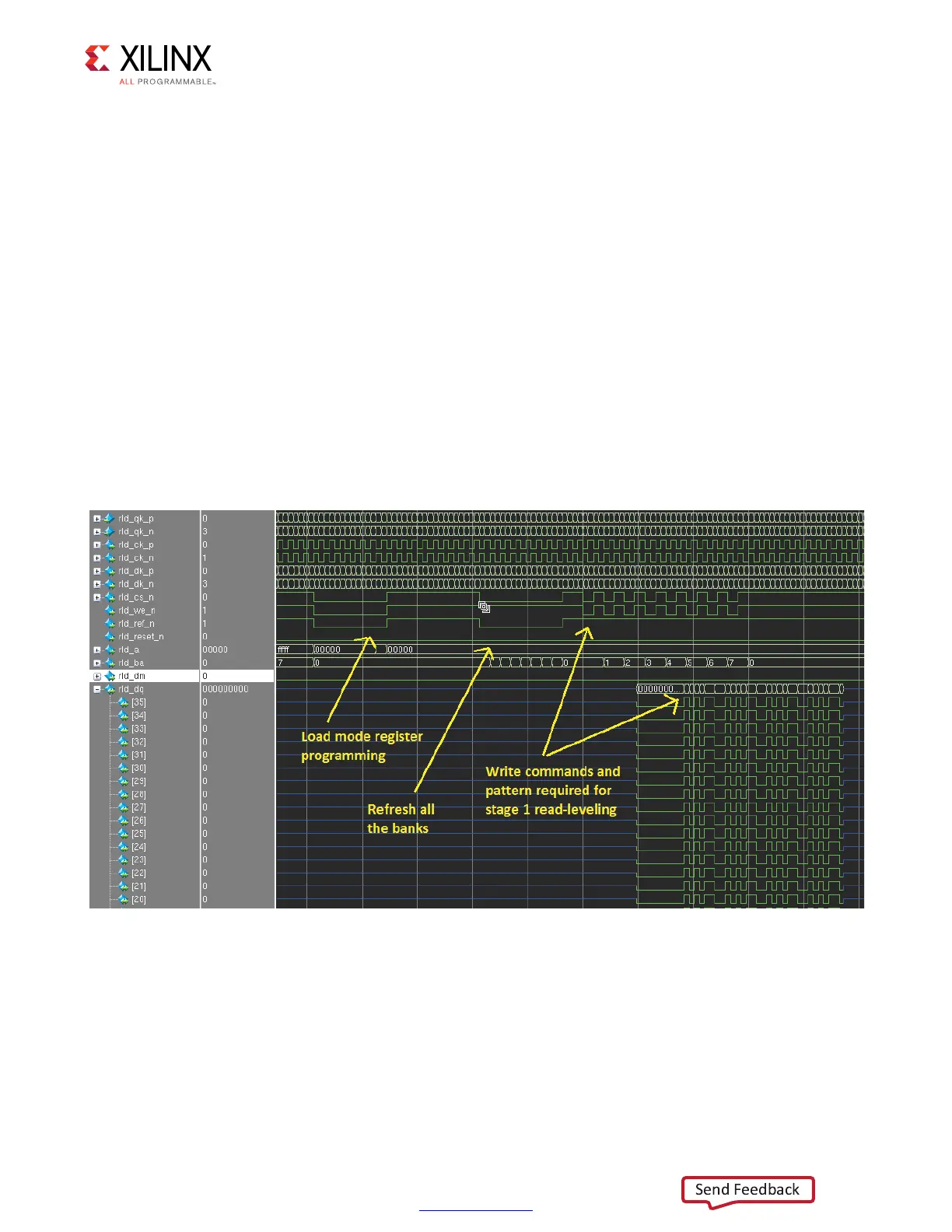

The first stage performs per-bit read leveling calibration. The data pattern used during this

stage is 0_F_0_F_0_F_F_0. The data pattern is first written to the memory, as shown in

Figure 3-69.

X-Ref Target - Figure 3-69

Figure 3-69: Writes for First Stage Read Calibration

Loading...

Loading...