Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 577

UG586 November 30, 2016

www.xilinx.com

Chapter 4: LPDDR2 SDRAM Memory Interface Solution

User Interface

The UI is shown in Table 4-14 and connects to an FPGA user design to allow access to an

external memory device.

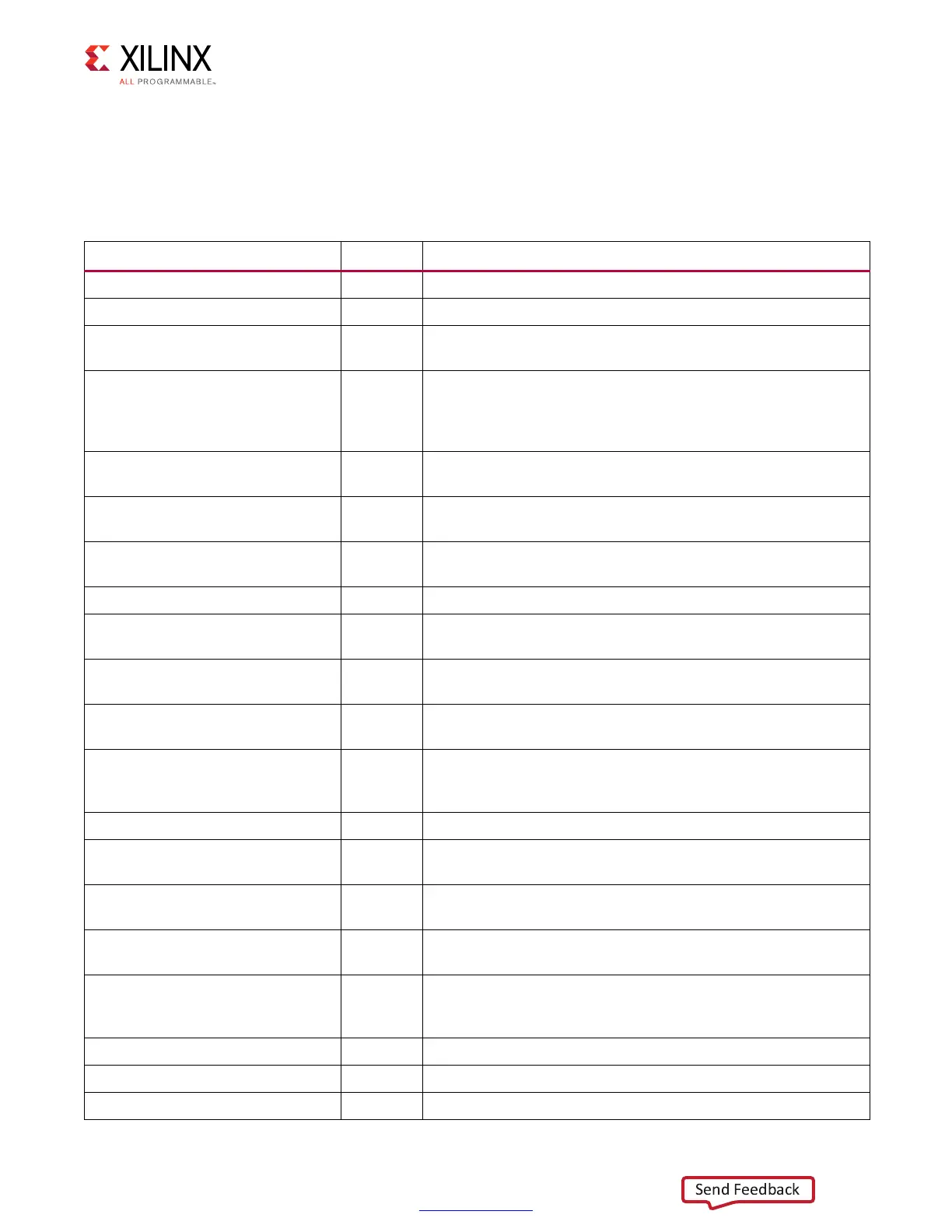

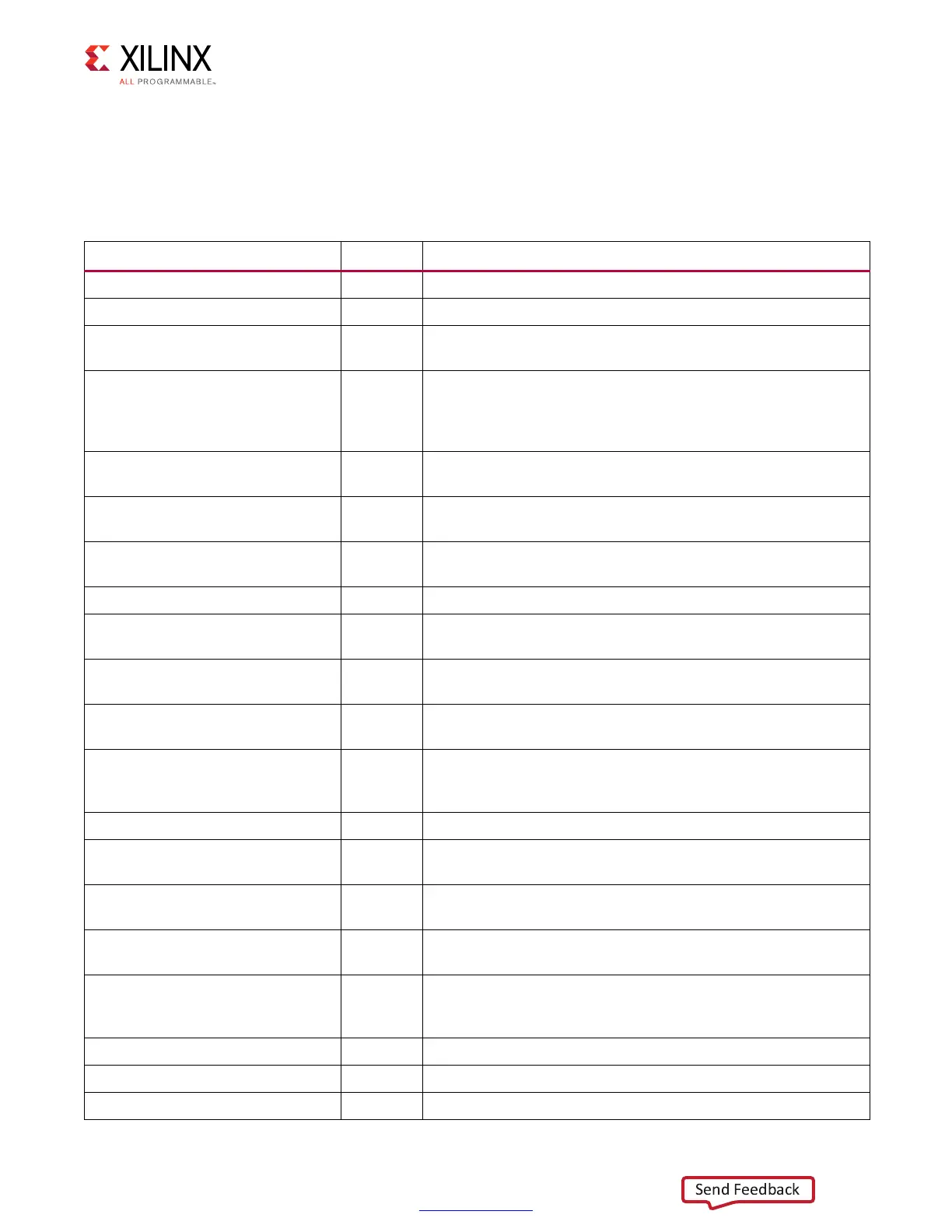

Table 4-14: User Interface

Signal Direction Description

app_addr[ADDR_WIDTH – 1:0] Input This input indicates the address for the current request.

app_cmd[2:0] Input This input selects the command for the current request.

app_en Input

This is the active-High strobe for the app_addr[], app_cmd[2:0],

and app_hi_pri inputs.

app_rdy Output

This output indicates that the UI is ready to accept commands.

If the signal is deasserted when app_en is enabled, the current

app_cmd and app_addr must be retried until app_rdy is

asserted.

app_hi_pri Input

This active-High input elevates the priority of the current

request.

app_rd_data

[APP_DATA_WIDTH – 1:0]

Output This provides the output data from read commands.

app_rd_data_end Output

This active-High output indicates that the current clock cycle is

the last cycle of output data on app_rd_data[].

app_rd_data_valid Output This active-High output indicates that app_rd_data[] is valid.

app_wdf_data

[APP_DATA_WIDTH – 1:0]

Input This provides the data for write commands.

app_wdf_end Input

This active-High input indicates that the current clock cycle is

the last cycle of input data on app_wdf_data[].

app_wdf_mask

[APP_MASK_WIDTH – 1:0]

Input This provides the mask for app_wdf_data[].

app_wdf_rdy Output

This output indicates that the write data FIFO is ready to receive

data. Write data is accepted when app_wdf_rdy = 1’b1 and

app_wdf_wren = 1’b1.

app_wdf_wren Input This is the active-High strobe for app_wdf_data[].

app_ref_req Input

This active-High input requests that a refresh command be

issued to the DRAM.

app_ref_ack Output

This active-High output indicates that the Memory Controller

has sent the requested refresh command to the PHY interface.

app_zq_req Input

This active-High input requests that a ZQ calibration command

be issued to the DRAM.

app_zq_ack Output

This active-High output indicates that the Memory Controller

has sent the requested ZQ calibration command to the PHY

interface.

ui_clk Output This UI clock must be a half or quarter of the DRAM clock.

init_calib_complete Output PHY asserts init_calib_complete when calibration is finished.

ui_clk_sync_rst Output This is the active-High UI reset.

Loading...

Loading...