Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 72

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

5: DGEN_WALKING1. Walking 1s are on the DQ pins. The starting position of 1 depends

on the address value.

6: DGEN_WALKING0. Walking 0s are on the DQ pins. The starting position of 0 depends

on the address value.

7: DGEN_PRBS. A 32-stage LFSR generates random data and is seeded by the starting

address. This data mode only works with PRBS address mode or Sequential address

mode.

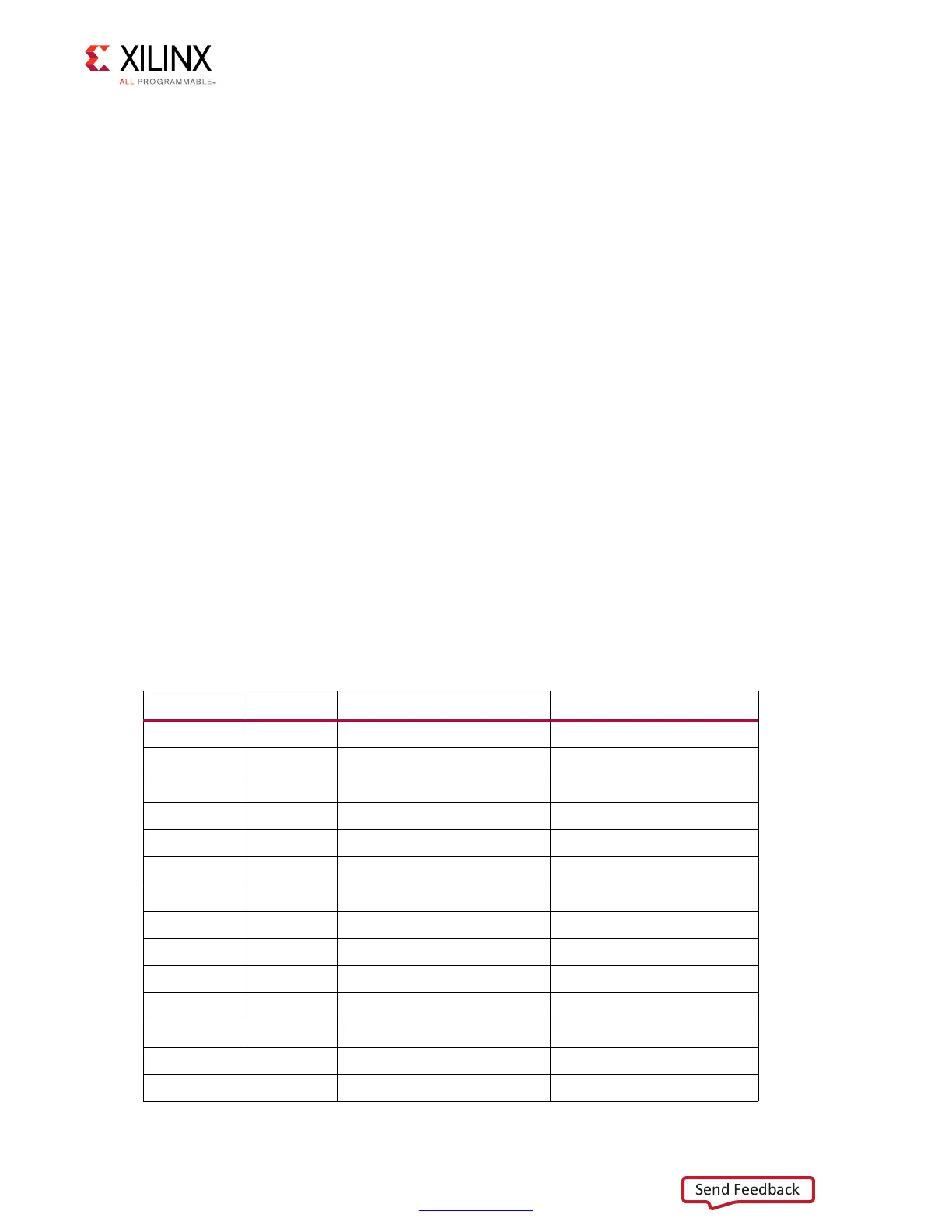

Modifying Port Address Space

The address space for a port can be modified by changing the BEGIN_ADDRESS and

END_ADDRESS parameters found in the top-level test bench file. These two values must be

set to align to the port data width. The two additional parameters, PRBS_SADDR_MASK_POS

and PRBS_EADDR_MASK_POS, are used in the default PRBS address mode to ensure that

out-of-range addresses are not sent to the port. PRBS_SADDR_MASK_POS creates an OR

mask that shifts PRBS-generated addresses with values below BEGIN_ADDRESS up into the

valid address space of the port. PRBS_SADDR_MASK_POS should be set to a 32-bit value

equal to the BEGIN_ADDRESS parameter. PRBS_EADDR_MASK_POS creates an AND mask

that shifts PRBS-generated addresses with values above END_ADDRESS down into the valid

address space of the port. PRBS_EADDR_MASK_POS should be set to a 32-bit value, where

all bits above the most-significant address bit of END_ADDRESS are set to 1 and all

remaining bits are set to 0. Table 1-12 shows some examples of setting the two mask

parameters.

Table 1-12: Example Settings for Address Space and PRBS Masks

SADDR EADDR PRBS_SADDR_MASK_POS PRBS_EADDR_MASK_POS

0x1000 0xFFFF 0x00001000 0xFFFF0000

0x2000 0xFFFF 0x00002000 0xFFFF0000

0x3000 0xFFFF 0x00003000 0xFFFF0000

0x4000 0xFFFF 0x00004000 0xFFFF0000

0x5000 0xFFFF 0x00005000 0xFFFF0000

0x2000 0x1FFF 0x00002000 0xFFFFE000

0x2000 0x2FFF 0x00002000 0xFFFFD000

0x2000 0x3FFF 0x00002000 0xFFFFC000

0x2000 0x4FFF 0x00002000 0xFFFF8000

0x2000 0x5FFF 0x00002000 0xFFFF8000

0x2000 0x6FFF 0x00002000 0xFFFF8000

0x2000 0x7FFF 0x00002000 0xFFFF8000

0x2000 0x8FFF 0x00002000 0xFFFF0000

0x2000 0x9FFF 0x00002000 0xFFFF0000

Loading...

Loading...