Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 330

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

PHY Control Block

The QDR PHY uses the PHY Control block to interface to the OUT_FIFOs and

PHASER_OUT_PHY. The PHY Control block helps to prevent the condition where one or

more of the OUT_FIFOs are operating close to the EMPTY condition of the OUT_FIFO, which

could potentially make the OUT_FIFO go EMPTY (based on how the WRCLK and RDCLK are

aligned at the OUT_FIFO over voltage-temperature variations) thereby causing the

OUT_FIFO to stall. The PHY Control block helps the OUT_FIFO to operate closer to the FULL

condition of the OUT_FIFO.

The steps required for the initialization are as follows:

1. After PHY_CONTROL_READY is asserted, PHY_CONTROL is programmed with a large

delay into the pc_phy_counters. The control word format is shown in Table 2-10 and

Table 2-11.

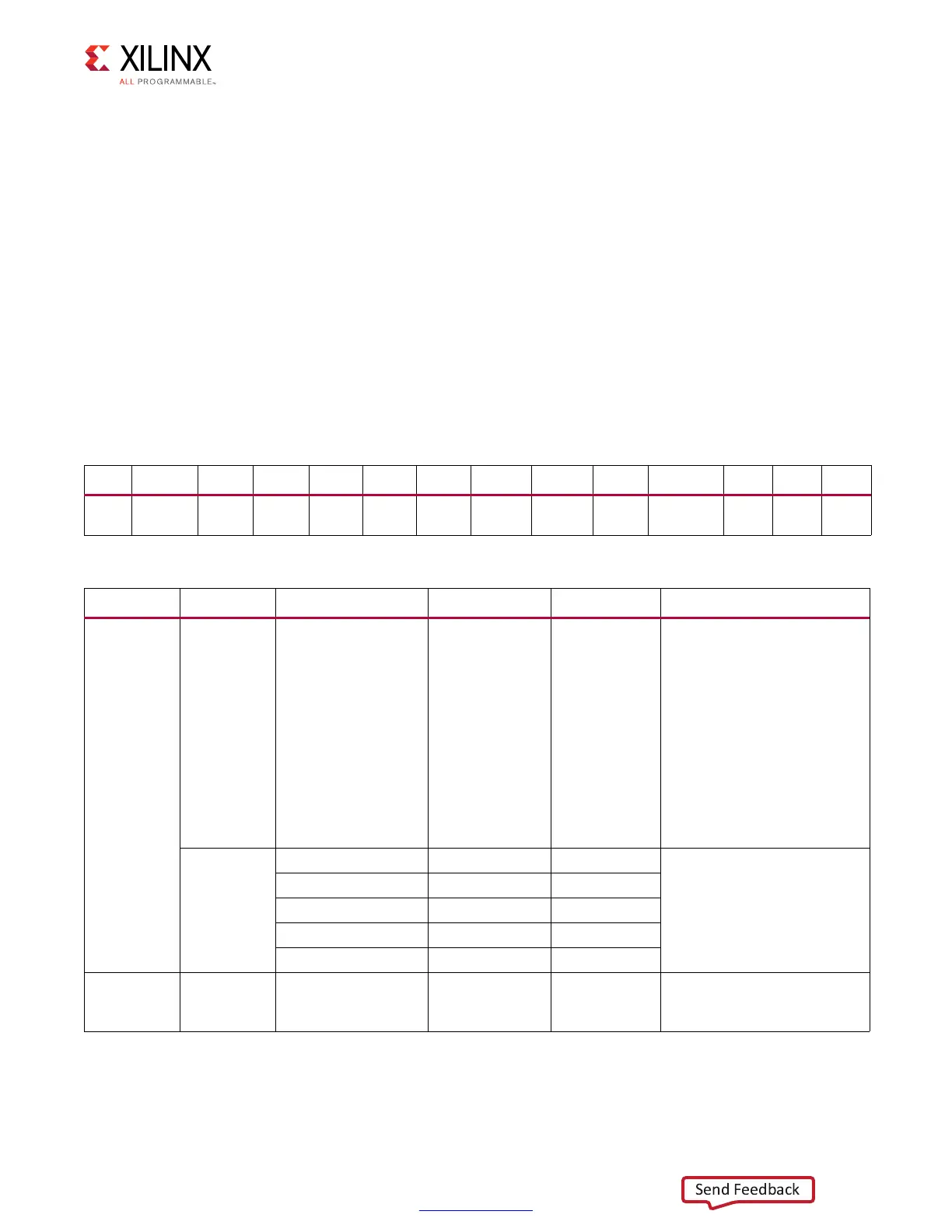

Table 2-10: Control Word Format

Bits 35:32 31 30 29:25 24:23 22:17 16:15 14:12 11:8 7:3 2 1 0

Field AO1

Major

OP

Minor

OP

Event

Delay

Seq

Data

Offset

IndexHi

(Rank)

IndexLo

(Bank)

AO0

Command

Offset

Non-

Data

Read Data

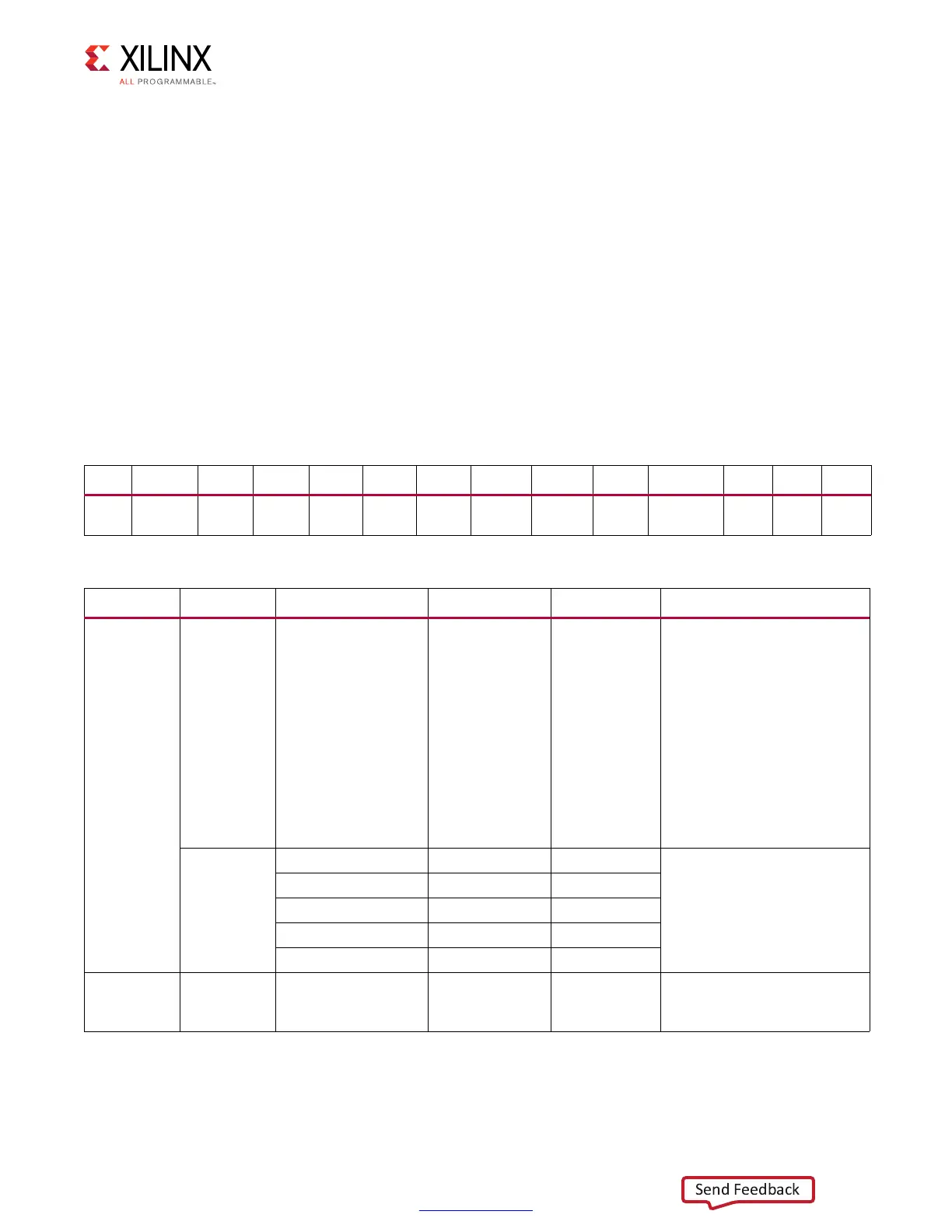

Table 2-11: Control Word Decode

MajorOP MinorOP EventDelay IndexHi IndexLo Registers

0–REGPRE

0 – REG Register Data[4:0]

IndexHi[16] =

Register Data[5]

IndexHi[15] =

Register Addr[3]

Register

Address Bits

[2:0]

4'b0000–4'b0011: Reserved

4'b0100: CTLCORR

4'b0101: RRDCNTR

4'b0110: REF2ACT

4'b0111: TFAW

4'b1000: A2ARD

4'b1001: A2AWR

4'b1010: PRE2ACT

4'b1011: ACT2PRE

4'b1100: RDA2ACT

4'b1101: RD2PRE

4'b1110: WRA2ACT

4'b1111: WR2PRE

1 – PRE

5'b000xx – STALL DC DC

The STALL operation delays the

issue of the Ready signal from

pc_phy_counters to the

sequencing state machines.

5'b010xx – REF Rank DC

5'b100xx – PREBANK Rank Bank

5'b110xx – PREALL Rank DC

All others – NOP DC DC

1–ACTRDWR ACT

29:28: ACT Slot

27: AP

26:25: RDWR Slot

Rank Bank

Loading...

Loading...