Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 253

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Debugging Write Calibration Failures (dbg_wrcal_err = 1)

Calibration Overview

Write calibration is required to align DQS to the correct CK edge. During write leveling, DQS

is aligned to the nearest rising edge of CK. However, this might not be the edge that

captures the write command.

Depending on the interface type (UDIMM, RDIMM, or component), the DQS could either be

one CK cycle earlier than, two CK cycles earlier than, or aligned to the CK edge that captures

the write command.

This is a pattern based calibration; hence, multiple writes followed by a single read are

issued during this stage. The following data patterns might be seen:

• On-time write pattern read back – FF00AA5555AA9966

•One CK early write pattern read back – AA5555AA9966BB11

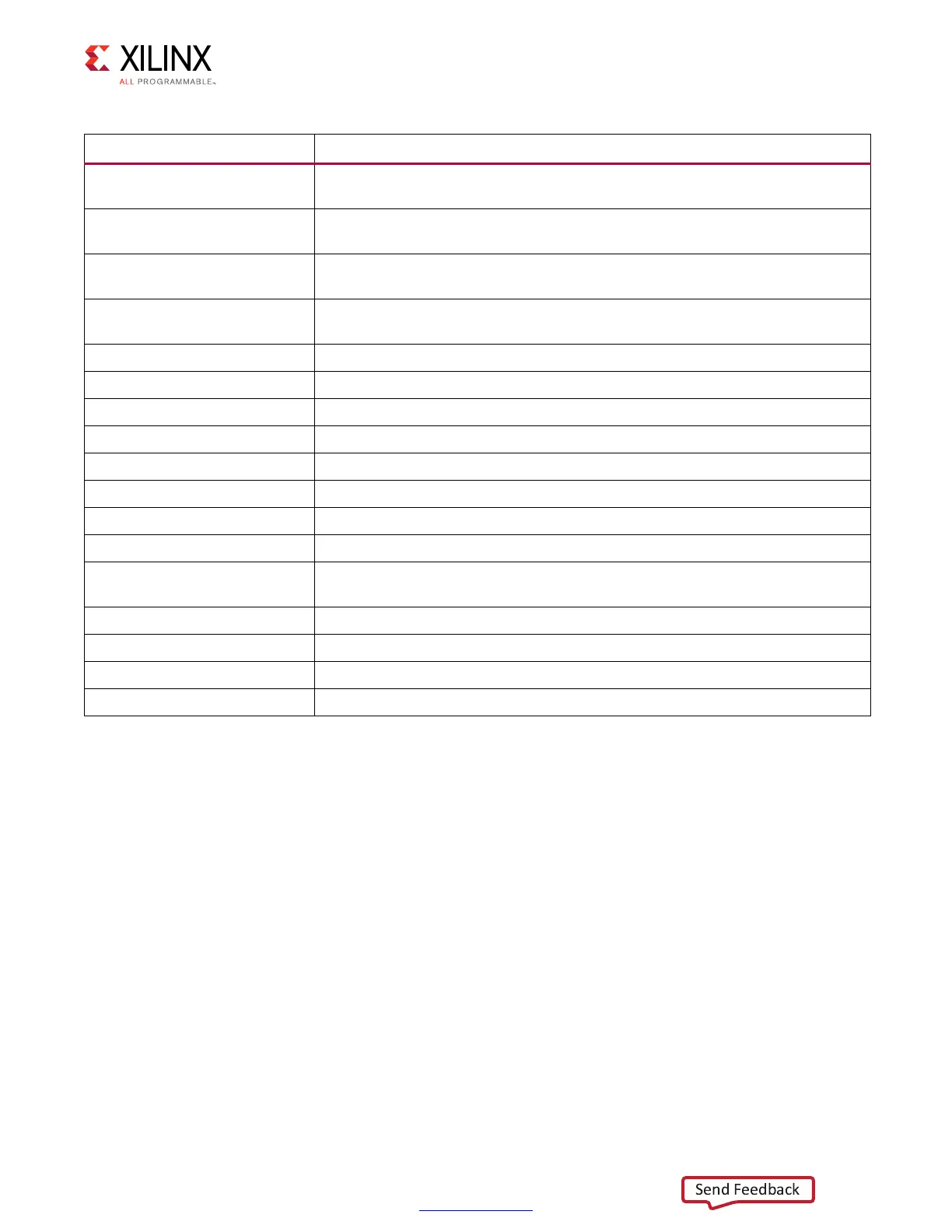

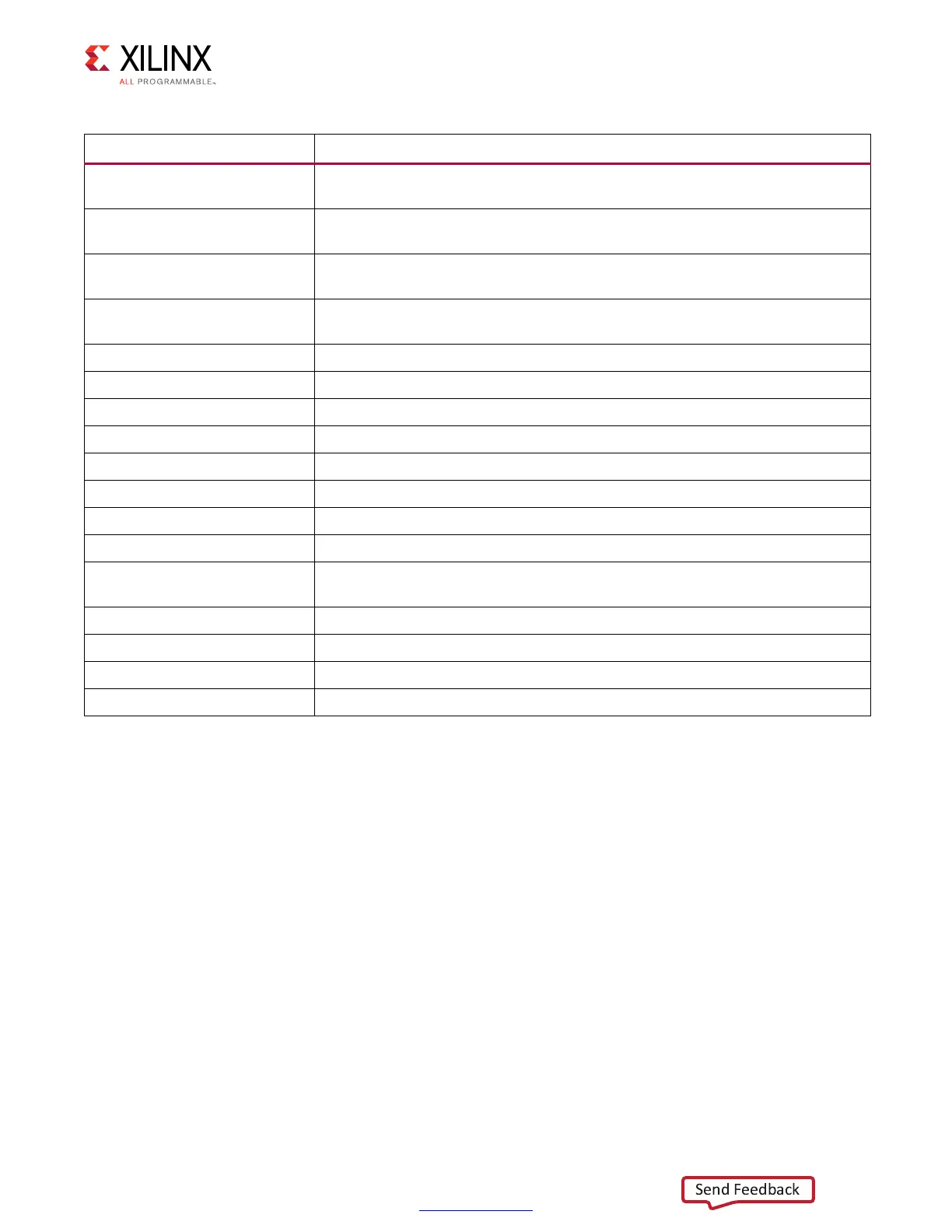

dbg_phy_oclkdelay_zfo[0]

1 indicates that the left-edge of the fall window was detected and it validates

fuzz2oneeighty as the tap value of the left-edge of the fall window.

dbg_phy_oclkdelay_zfo[1]

1 indicates that the left-edge of the rise window was detected and it validates

fuzz2zero as the tap value of the left-edge of the rise window.

dbg_phy_oclkdelay_zfo[2]

1 indicates that the right-edge of the fall window was detected and it validates

oneeighty2fuzz as the tap value of the right-edge of the fall window.

dbg_phy_oclkdelay_zfo[3]

1 indicates that the right-edge of the rise window was detected and it validates

zero2fuzz as the tap value of the right-edge of the rise window.

dbg_ocal_fuzz2oneeighty Stage 3 tap value of the left-edge of the fall window.

dbg_ocal_fuzz2zero Stage 3 tap value of the left-edge of the rise window.

dbg_ocal_oneeighty2fuzz Stage 3 tap value of the right-edge of the fall window.

dbg_ocal_zero2fuzz Stage 3 tap value of the right-edge of the rise window.

dbg_ocal_oclkdelay_calib_cnt Byte count indicating the byte being calibrated.

dbg_ocal_lim_done Indicates that stage 3 lower and upper limits have been determined.

dbg_ocal_stg3_lim_left Stage 3 lower limit

dbg_ocal_stg3_lim_right Stage 3 upper limit

phy_oclkdelay_cal_taps

Final stage 3 tap values for all the bytes in the interface. Bits[5:0] for byte 0 and

Bits[11:6] for byte 1.

dbg_ocal_center_calib_start Indicates end of edge detection and start of centering in valid window.

dbg_ocal_center_calib_done Indicates end of the centering stage of calibration.

dbg_ocal_tap_cnt Stage 3 tap value during calibration for each group.

dbg_ocal_scan_win_not_found 1 indicates that window edge is not found.

Table 1-78: Debug Signals of Interest for OCLKDELAYED Calibration (Cont’d)

Signal Name Description

Loading...

Loading...