Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 397

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

Extended FPGA Options

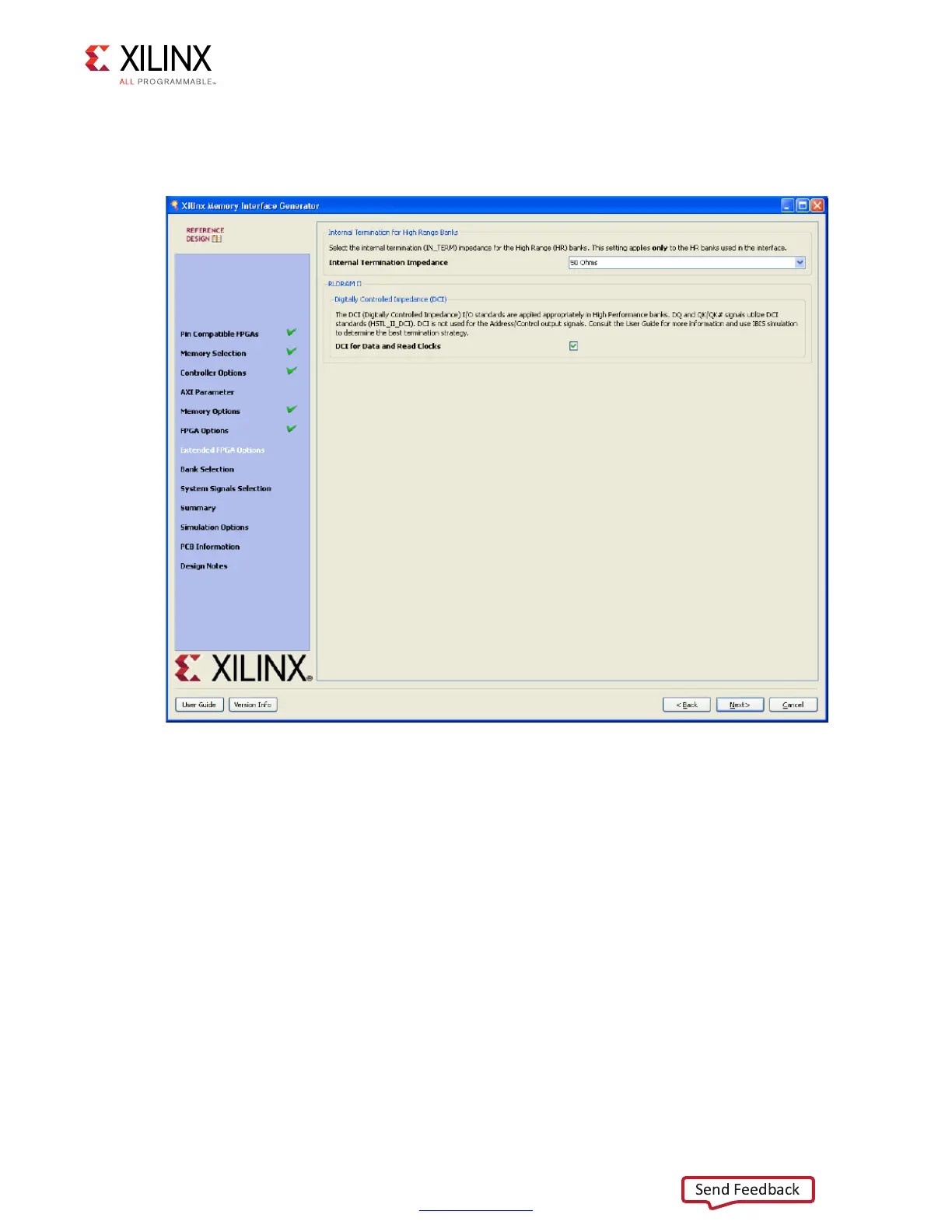

Figure 3-21 shows the Extended FPGA Options page.

• Digitally Controlled Impedance (DCI) – When selected, this option internally

terminates the signals from the RLDRAM II read path. DCI is available in the High

Performance Banks.

• Internal Termination for High Range Banks – The internal termination option can be

set to 40, 50, or 60Ω or disabled. This termination is for the RLDRAM II and RLDRAM 3

read path. This selection is only for High Range banks.

Bank Selection

This feature allows the selection of bytes for the memory interface. Bytes can be selected

for different classes of memory signals, such as:

• Address and control signals

• Data Read signals

• Data Write signals

X-Ref Target - Figure 3-21

Figure 3-21: Extended FPGA Options Page

Loading...

Loading...