Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 548

UG586 November 30, 2016

www.xilinx.com

Chapter 4: LPDDR2 SDRAM Memory Interface Solution

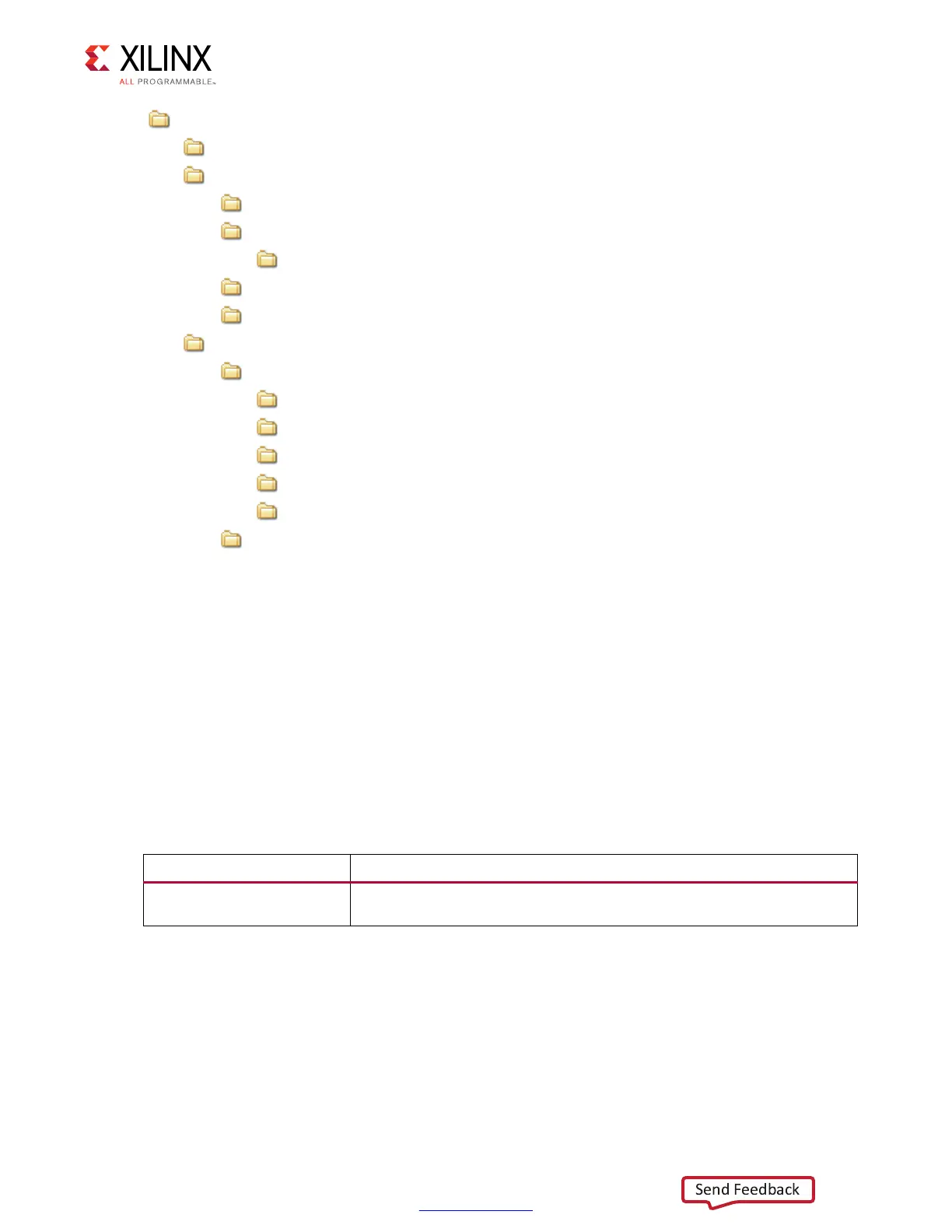

mig_7series_v4_1

docs

example_design

par

rtl

traffic_gen

sim

synth

user_design

rtl

clocking

controller

ip_top

phy

ui

xdc

Directory and File Contents

The 7 series FPGAs core directories and their associated files are listed in this section for

Vivado implementations.

<component name>/example_design/

The example_design folder contains four folders, namely, par, rtl, sim, and synth.

example_design/rtl

This directory contains the example design (Table 4-1).

Table 4-1: Files in example_design/rtl Directory

Name Description

example_top.v

This top-level module serves as an example for connecting the user

design to the 7 series FPGAs memory interface core.

Loading...

Loading...