Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 250

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

Debug

• If this stage of calibration failed with the assertion of dbg_rdlvl_err[1], set the ILA

trigger to dbg_rdlvl_err[1].

• If this stage of calibration was successful and the results need to be analyzed, use the

trigger dbg_rdlvl_done[1] = R.

• Set the VIO dbg_dqs for each byte and capture the following signals; the results for

each byte should be captured in the “7 Series DDR3 Calibration Results” spreadsheet.

Later releases of the MIG tool include results for all DQS byte groups removing the need

to use dbg_dqs

.

• Always look at DQ[0] for each component. Memory devices either send the “01010101”

or “10101010” pattern on all DQ bits or on DQ[0] as specified by the JEDEC standard.

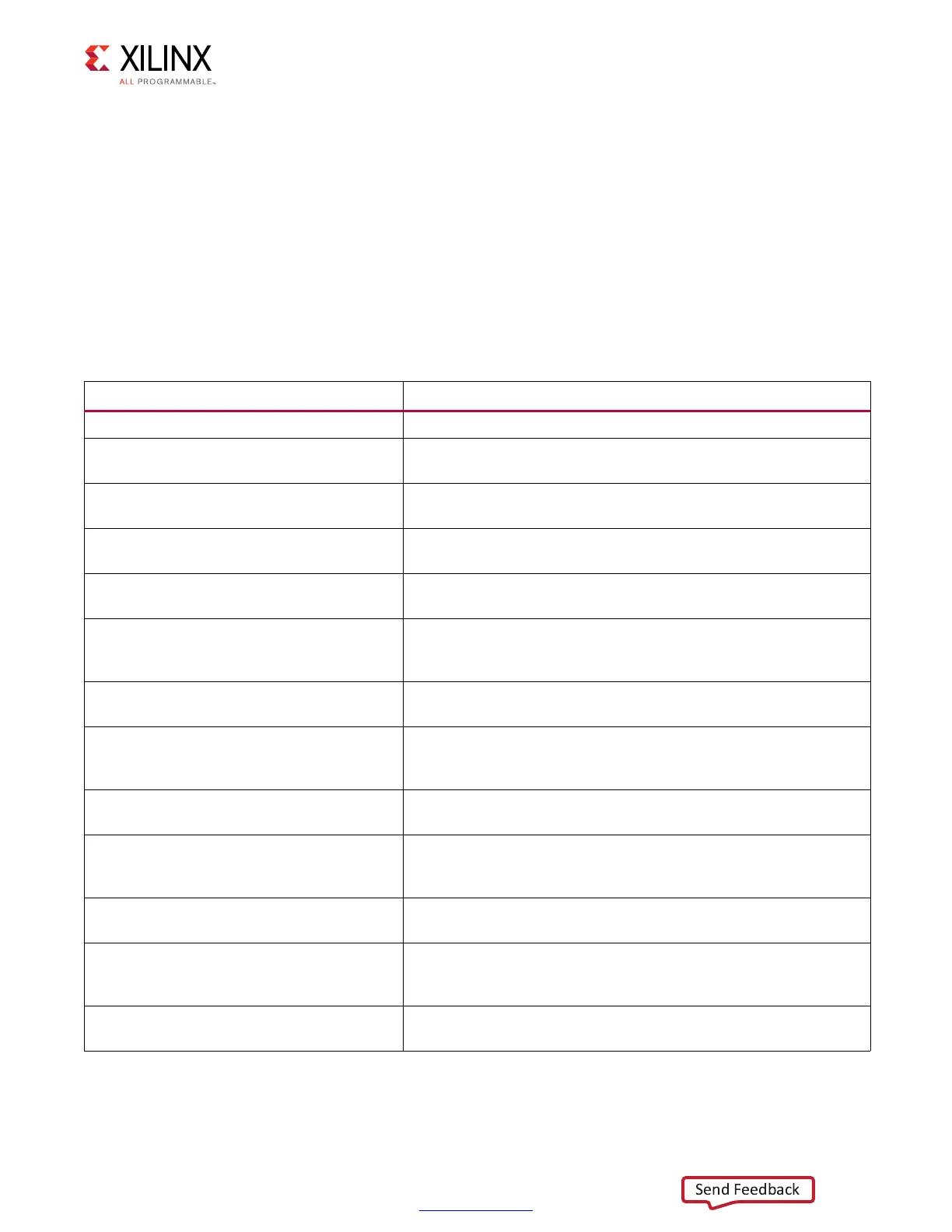

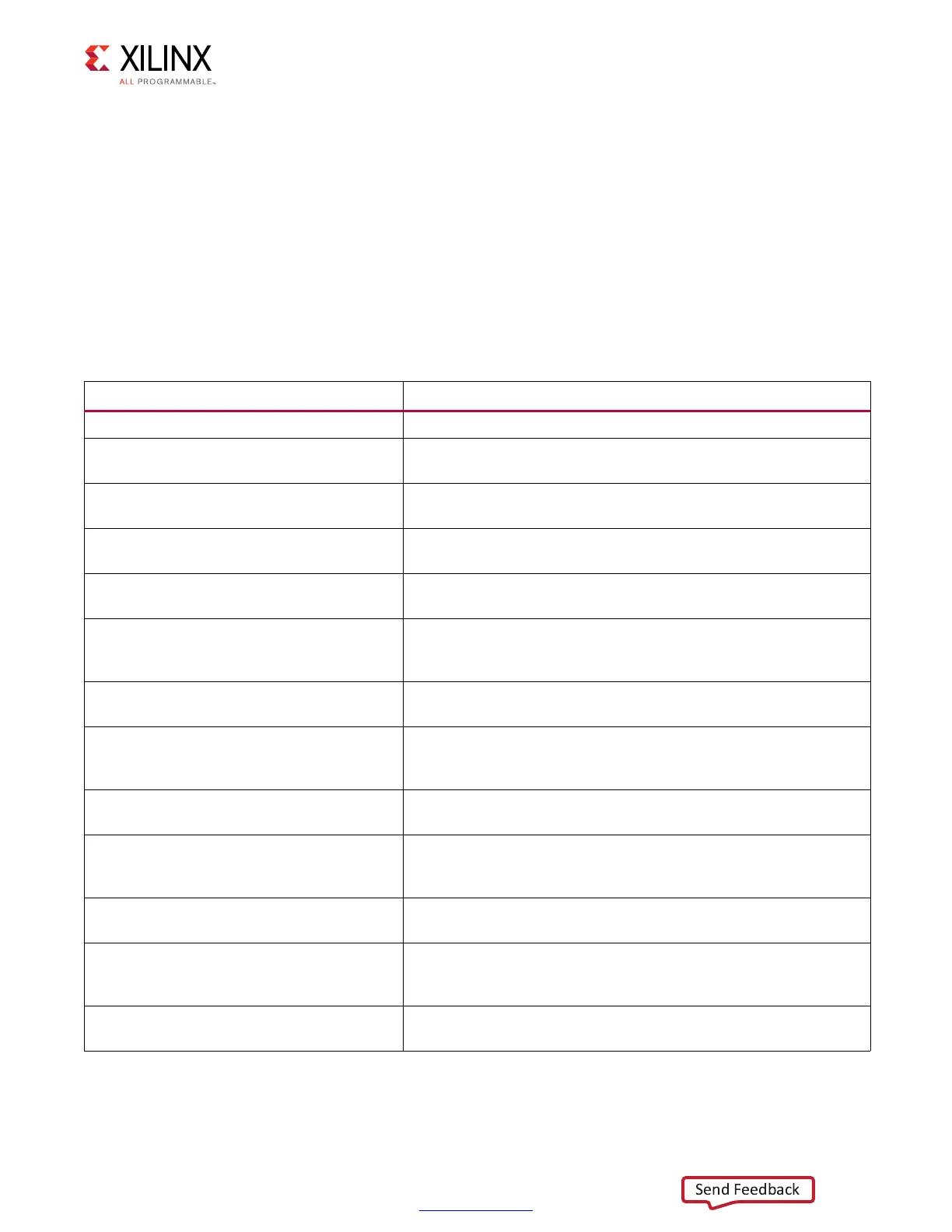

Table 1-77: Debug Signals of Interest for MPR Read Leveling Calibration

Signal Name Description

dbg_rdlvl_start[1] Signifies the start of the MPR stage of calibration.

dbg_rdlvl_done[1]

Signifies the successful completion of the MPR Stage of

calibration.

dbg_rdlvl_err[1]

Signifies the MPR stage of calibration exhibited errors and did not

complete.

cal1_state_r

State machine variable for MPR and Read Leveling Stage 1. States

can be decoded in the ddr_phy_rdlvl.v module.

cal1_cnt_cpt_r

Signifies the byte that failed MPR read leveling or read leveling

stage 1.

dbg_cpt_first_edge_cnt_by_dqs

Signifies PHASER_IN fine tap count when the first edge in MPR

and Read Leveling Stage 1 is found. Byte capture based on VIO

dbg_dqs setting.

dbg_cpt_first_edge_cnt

Signifies PHASER_IN fine tap count when the first edge in MPR

and Read Leveling Stage 1 is found.

dbg_cpt_second_edge_cnt_by_dqs

Signifies PHASER_IN fine tap count when then second edge in

MPR and Read Leveling Stage 1 is found. Byte capture based on

VIO dbg_dqs setting.

dbg_cpt_second_edge_cnt

Signifies PHASER_IN fine tap count when then second edge in

MPR and Read Leveling Stage 1 is found.

dbg_cpt_tap_cnt_by_dqs

Signifies the center tap moved to based on when the first and

second edges were found. Byte capture based on VIO dbg_dqs

setting.

dbg_cpt_tap_cnt

Signifies the center tap moved to based on when the first and

second edges were found.

dbg_dq_idelay_tap_cnt_by_dqs

IDELAY tap value for MPR and Read Leveling Stage 1. This should

be within 2 to 3 taps across all DQS byte groups. Byte capture

based on VIO dbg_dqs setting.

dbg_dq_idelay_tap_cnt

IDELAY tap value for MPR and Read Leveling Stage 1. This should

be within 2 to 3 taps across all DQS byte groups.

Loading...

Loading...