Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 61

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

user_design/rtl/clocking

This directory contains the user design (Table 1-5).

user_design/rtl/controller

This directory contains the Memory Controller that is instantiated in the example design

(Table 1-6).

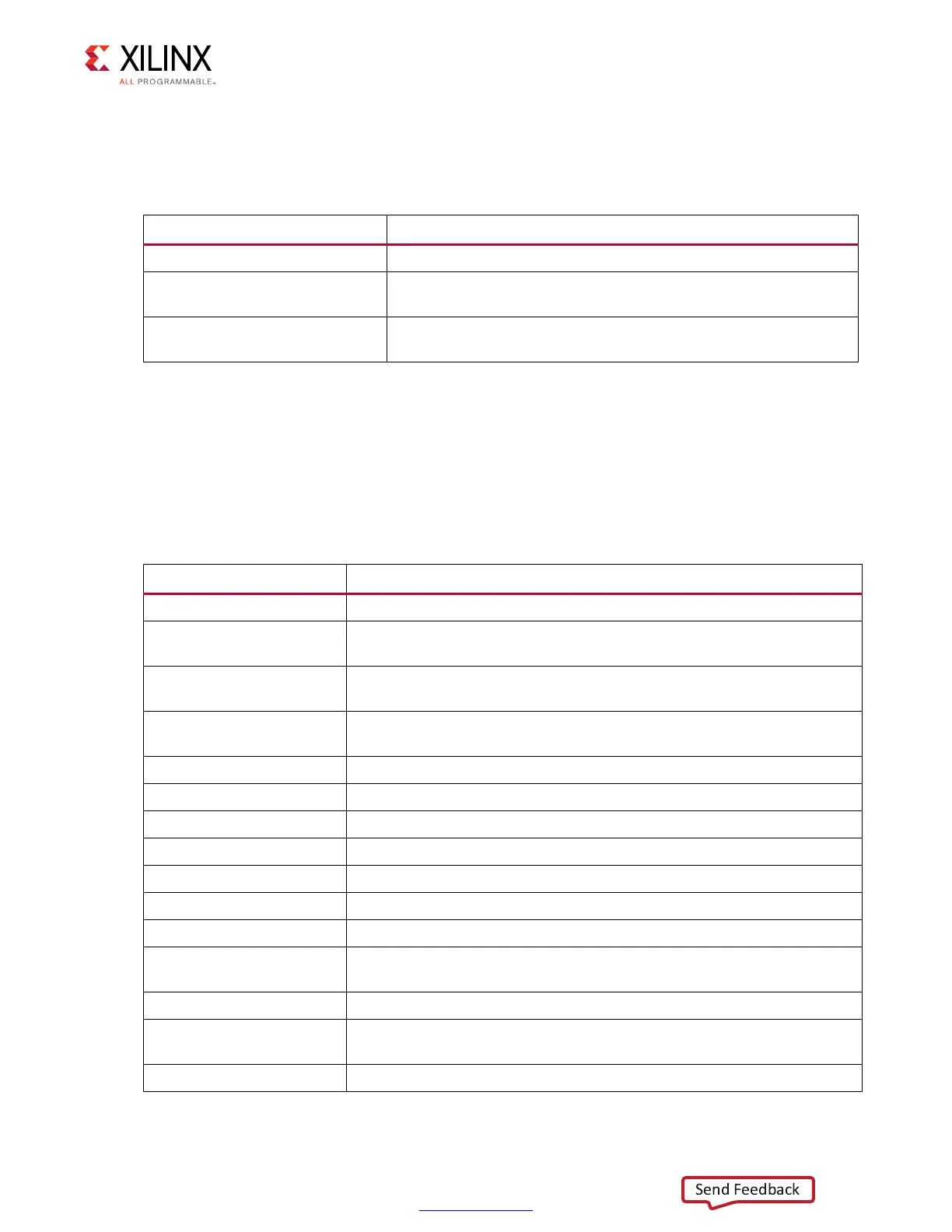

Table 1-5: Files in user_design/rtl/clocking Directory

Name

(1)

Description

clk_ibuf.v This module instantiates the input clock buffer.

iodelay_ctrl.v

This module instantiates IDELAYCNTRL primitives needed for

IDELAY use.

infrastructure.v

This module helps in clock generation and distribution, and reset

synchronization.

Notes:

1. All file names are prefixed with the MIG core version number. For example, for the MIG 4.1 release module name

of clk_ibuf in generated output is now mig_7series_v4_1_clk_ibuf.

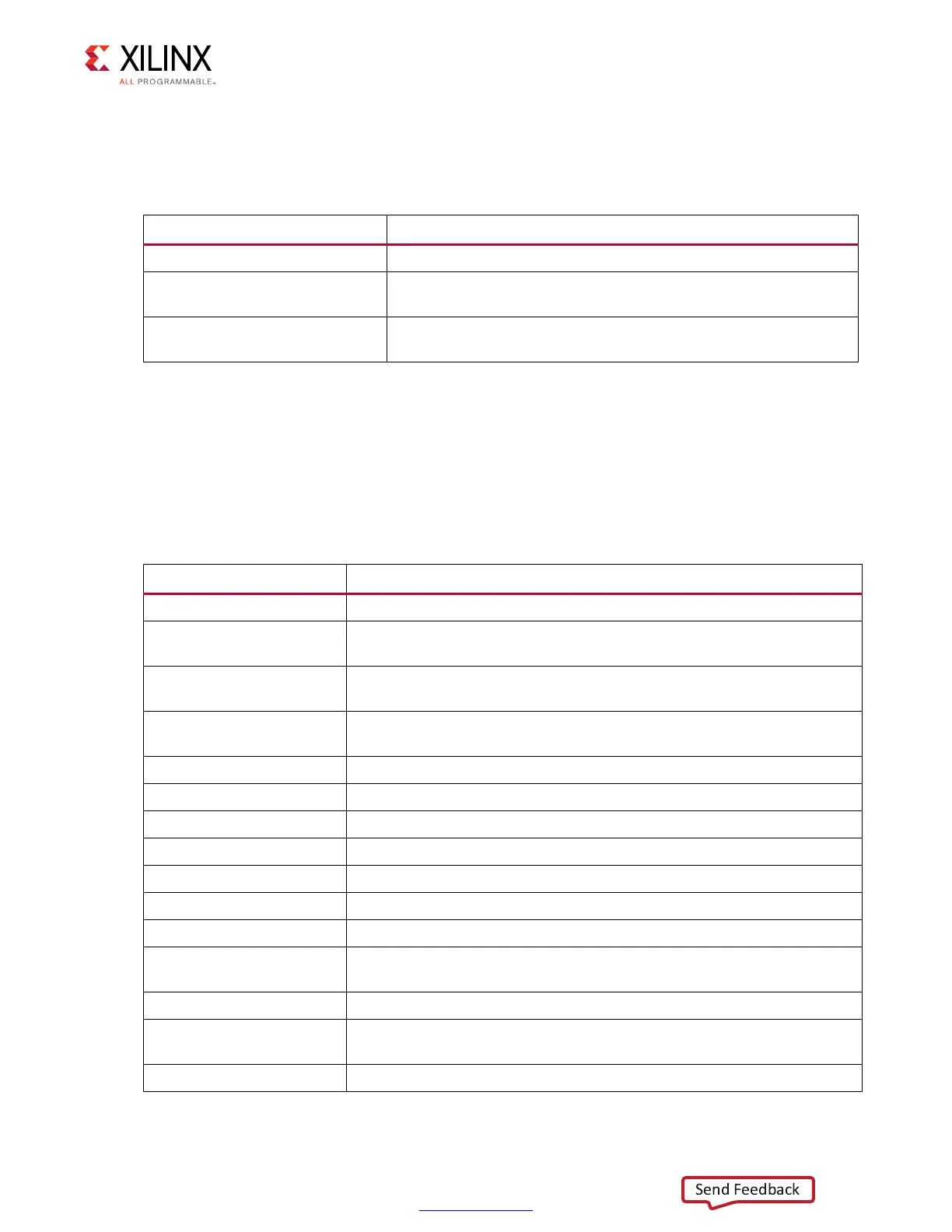

Table 1-6: Files in user_design/rtl/controller Directory

Name

(1)

Description

arb_mux.v This is the top-level module of arbitration logic.

arb_row_col.v

This block receives requests to send row and column commands from the

bank machines and selects one request, if any, for each state.

arb_select.v

This module selects a row and column command from the request

information provided by the bank machines.

bank_cntrl.v

This structural block instantiates the three subblocks that comprise the

bank machine.

bank_common.v This module computes various items that cross all of the bank machines.

bank_compare.v This module stores the request for a bank machine.

bank_mach.v This is the top-level bank machine block.

bank_queue.v This is the bank machine queue controller.

bank_state.v This is the primary bank state machine.

col_mach.v This module manages the DQ bus.

mc.v This is the top-level module of the Memory Controller.

mem_intfc.v

This top-level memory interface block instantiates the controller and the

PHY.

rank_cntrl.v This module manages various rank-level timing parameters.

rank_common.v

This module contains logic common to all rank machines. It contains a

clock prescaler and arbiters for refresh and periodic read.

rank_mach.v This is the top-level rank machine structural block.

Loading...

Loading...