Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 112

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

The register is only implemented if C_ECC_TEST = “ON” or ECC_TEST_FI_XOR = “ON” and

ECC = “ON” in a MIG design in the Vivado IP catalog.

Injecting faults should be performed in a critical region in software; that is, writing this

register and the subsequent write to the memory must not be interrupted.

Special consideration must be given across FI_D0, FI_D1, FI_D2, and FI_D3 such that only a

single error condition is introduced.

FI_D1

This register is used to inject errors in data (Bits[63:32]) written to memory and can be used

to test the error correction and error signaling. The bits set in the register toggle the

corresponding data bits (word 1 or Bits[63:32]) of the subsequent data written to the

memory without affecting the ECC bits written. After the fault has been injected, the Fault

Injection Data register is cleared automatically.

This register is only implemented if C_ECC_TEST = “ON” or ECC_TEST_FI_XOR = “ON” and

ECC = “ON” in a MIG design in the Vivado IP catalog.

Injecting faults should be performed in a critical region in software; that is, writing this

register and the subsequent write to the memory must not be interrupted.

FI_D2

Note: This register is only used when DQ_WIDTH =144.

This register is used to inject errors in data (Bits[95:64]) written to memory and can be used

to test the error correction and error signaling. The bits set in the register toggle the

corresponding data bits (word 2 or Bits[95:64]) of the subsequent data written to the

memory without affecting the ECC bits written. After the fault has been injected, the Fault

Injection Data register is cleared automatically.

This register is only implemented if C_ECC_TEST = “ON” or ECC_TEST_FI_XOR = “ON” and

ECC = “ON” in a MIG design in the Vivado IP catalog.

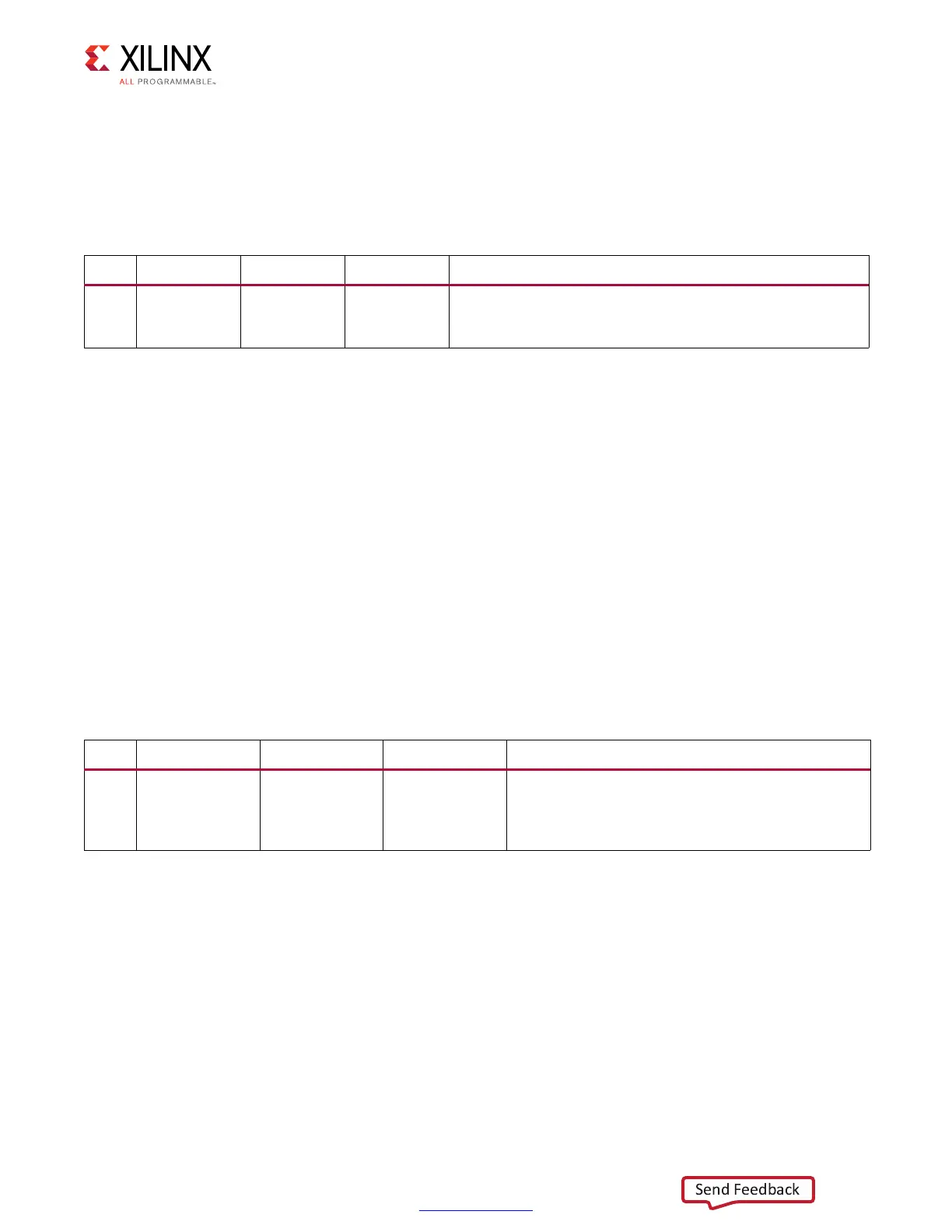

Table 1-44: Fault Injection Data (Word 0) Register Bit Definitions

Bits Name Core Access Reset Value Description

31:0 FI_D0 W 0

Bit positions set to 1 toggle the corresponding Bits[31:0] of

the next data word written to the memory. This register is

automatically cleared after the fault has been injected.

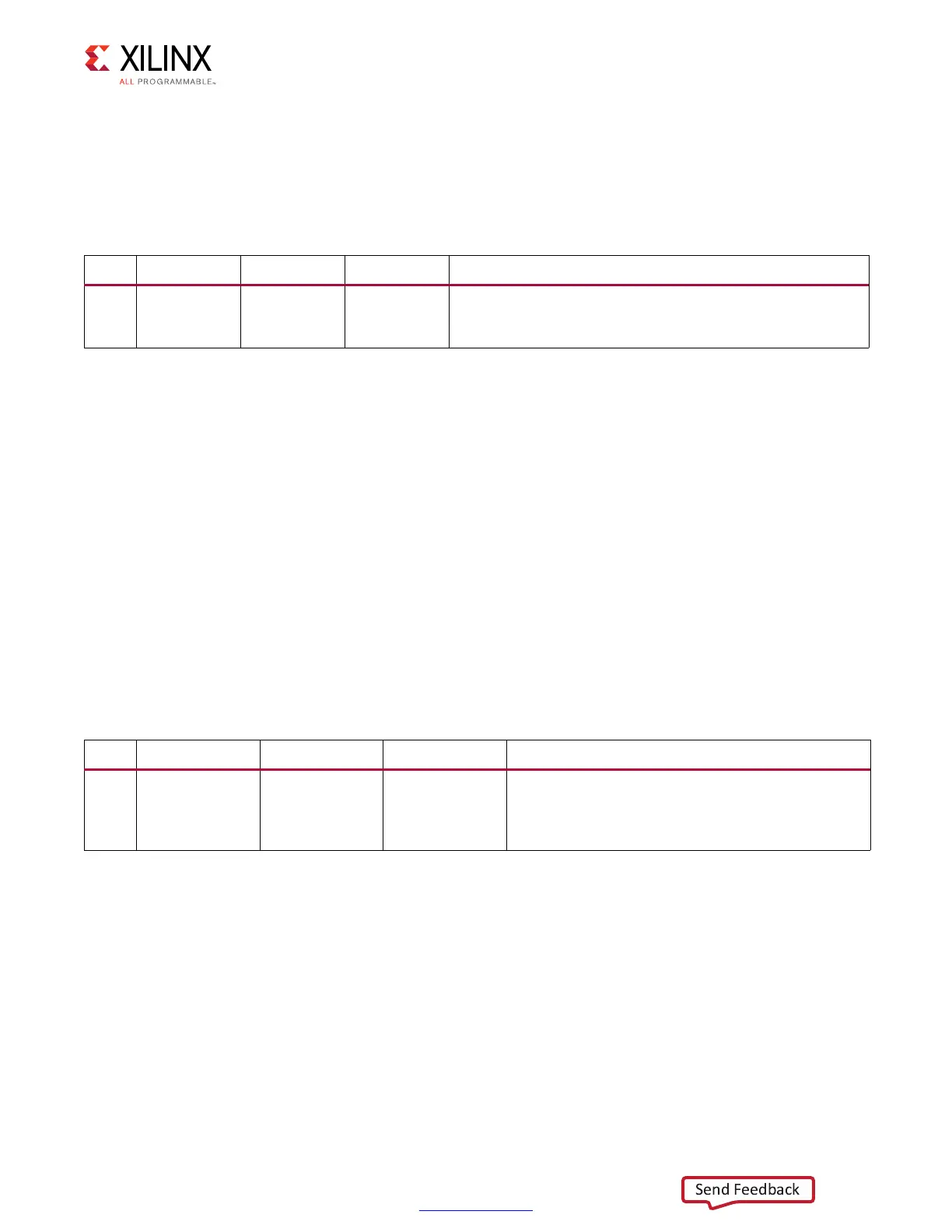

Table 1-45: Fault Injection Data (Word 1) Register Bit Definitions

Bits Name Core Access Reset Value Description

31:0 FI_D1 W 0

Bit positions set to 1 toggle the corresponding

Bits[63:32] of the next data word written to the

memory. This register is automatically cleared after

the fault has been injected.

Loading...

Loading...