Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 161

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

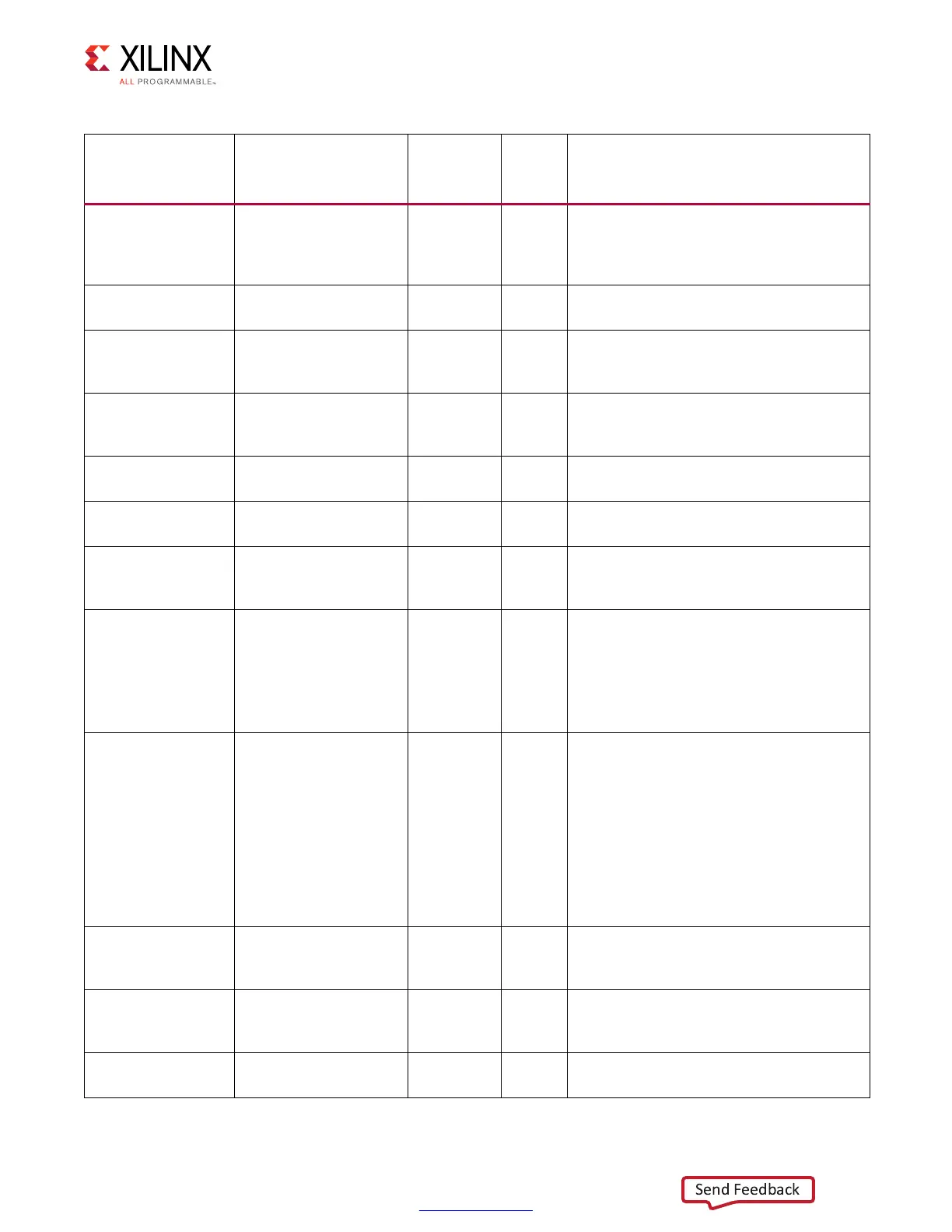

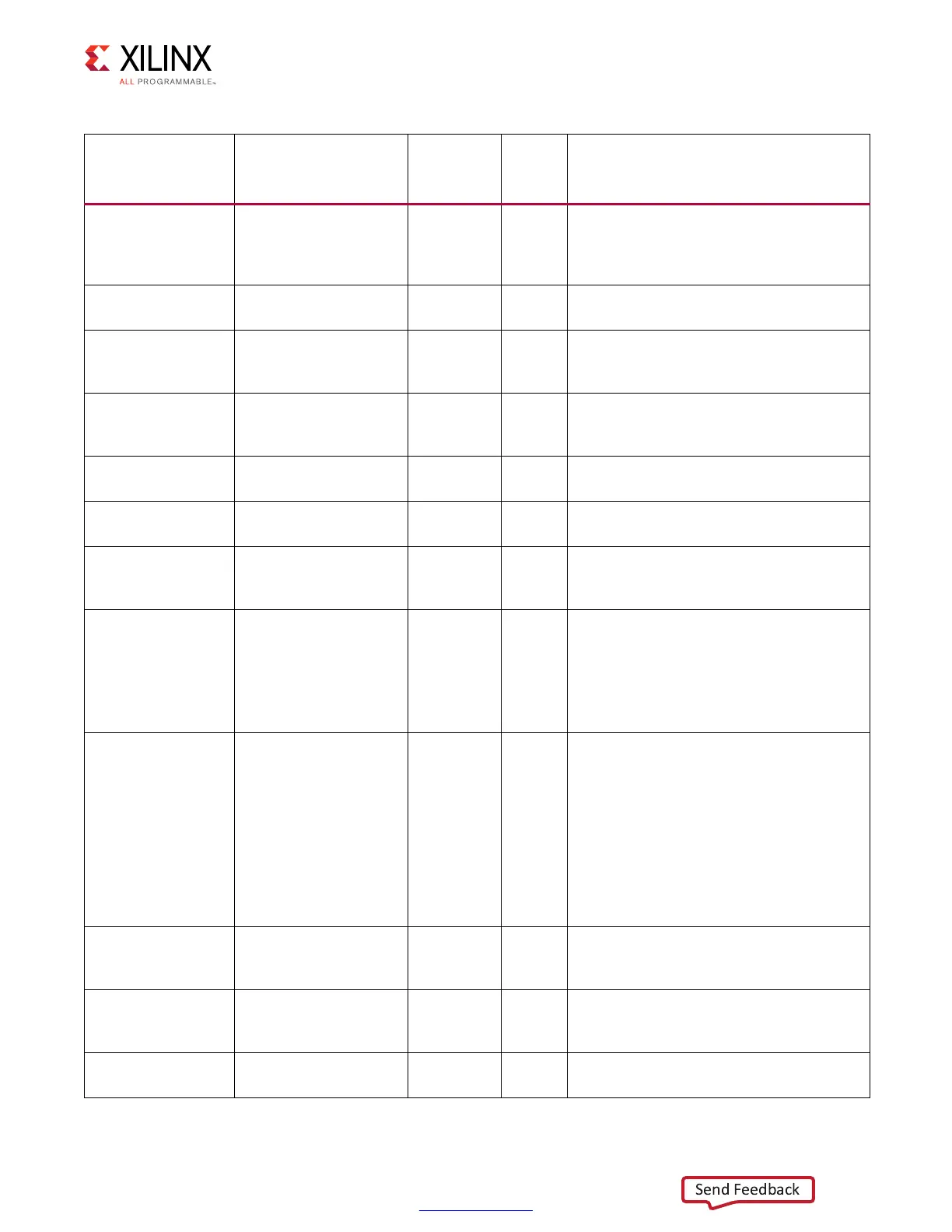

mc_cke [nCK_PER_CLK – 1:0] Input –

mc_cke [nCK_PER_CLK – 1:0] is the CKE

associated with the DRAM interface. This

signal is valid when the CKE_ODT_AUX

parameter is set to FALSE.

mc_reset_n 1 Input

Active-

Low

mc_reset_n is input directly to the

IOLOGIC without an OUT_FIFO.

mc_wrdata

[2 × nCK_PER_CLK ×

DQ_WIDTH – 1:0]

Input –

This is the write data to the dedicated PHY.

It is 8x the memory DQ width for a 4:1

clock ratio.

mc_wrdata_mask

[2 × nCK_PER_CLK ×

(DQ_WIDTH/8) – 1:0]

Input –

This is the write data mask to the

dedicated PHY. It is 8x the memory DM

width for a 4:1 clock ratio.

mc_wrdata_en 1 Input

Active-

High

This signal is the WREN input to the DQ

OUT_FIFO.

mc_cmd_wren 1 Input

Active-

High

This signal is the write enable input of the

address/command OUT_FIFOs.

mc_ctl_wren 1 Input

Active-

High

This signal is the write enable input to the

PHY control word FIFO in the dedicated

PHY block.

mc_cmd [2:0] Input –

This signal is used for PHY_Ctl_Wd

configuration:

0x04: Non-data command (No column

command in the sequence of commands)

0x01: Write command

0x03: Read command

mc_data_offset [5:0] Input –

This signal is used for PHY_Ctl_Wd

configuration:

0x00: Non-data command (No column

command in the sequence of commands)

CWL + COL cmd position + 2 (for

nCK_PER_CLK = 4) or CWL + COL cmd

position – 2 (for nCK_PER_CLK = 2): Write

command

calib_rd_data_offset+COL cmd position –

1: Read command

mc_aux_out0 [3:0] Input

Active-

High

This is the auxiliary outputs field in the

PHY control word used to control ODT and

CKE assertion.

mc_aux_out1 [3:0] Input

Active-

High

This is the auxiliary outputs field in the

PHY control word used to control ODT and

CKE assertion for four-rank interfaces.

mc_rank_cnt [1:0] Input –

This is the rank accessed by the command

sequence in the PHY control word.

Table 1-61: Memory Controller to Calibration Logic Interface Signals (Cont’d)

Signal Name Width

I/O

To/From

PHY

Type Description

Loading...

Loading...