Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 409

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

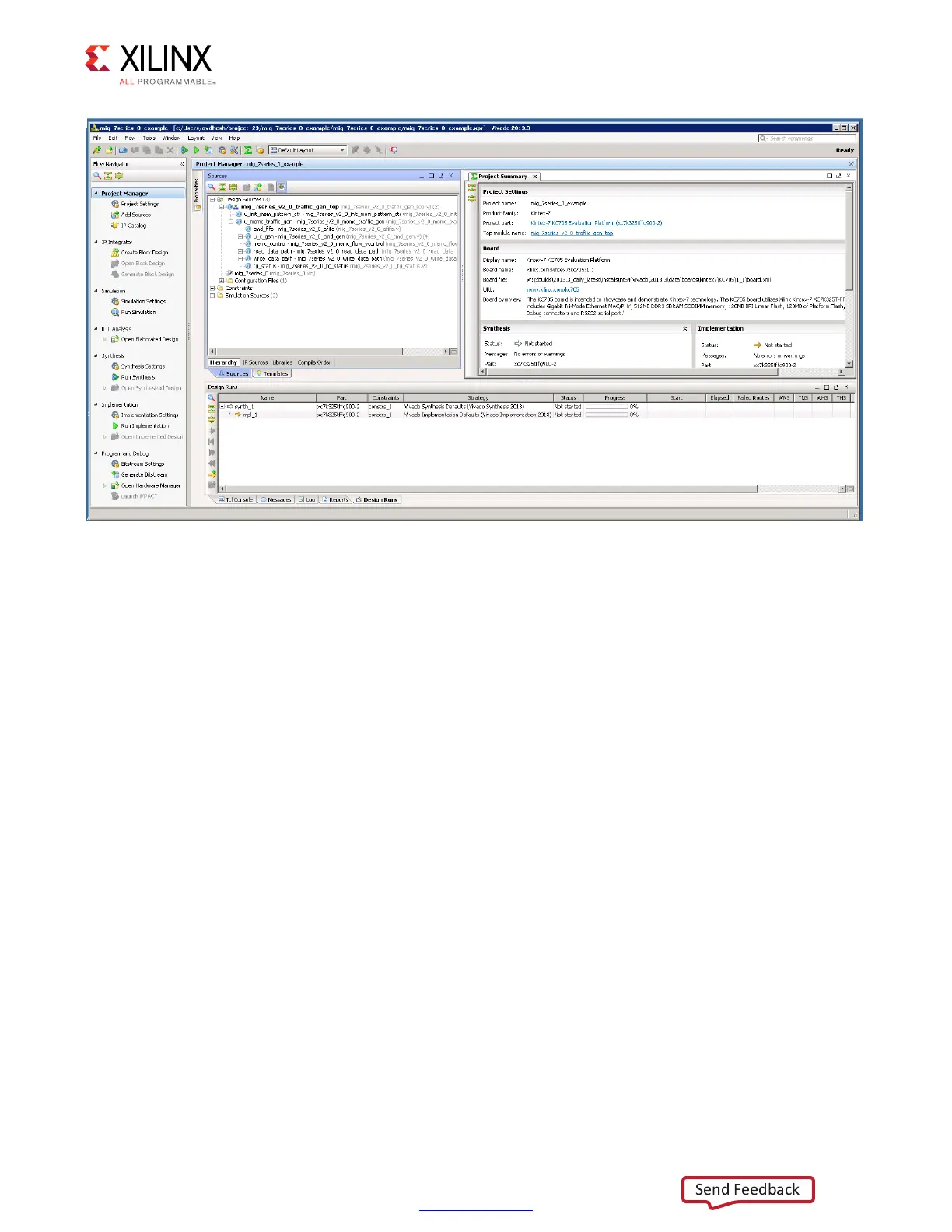

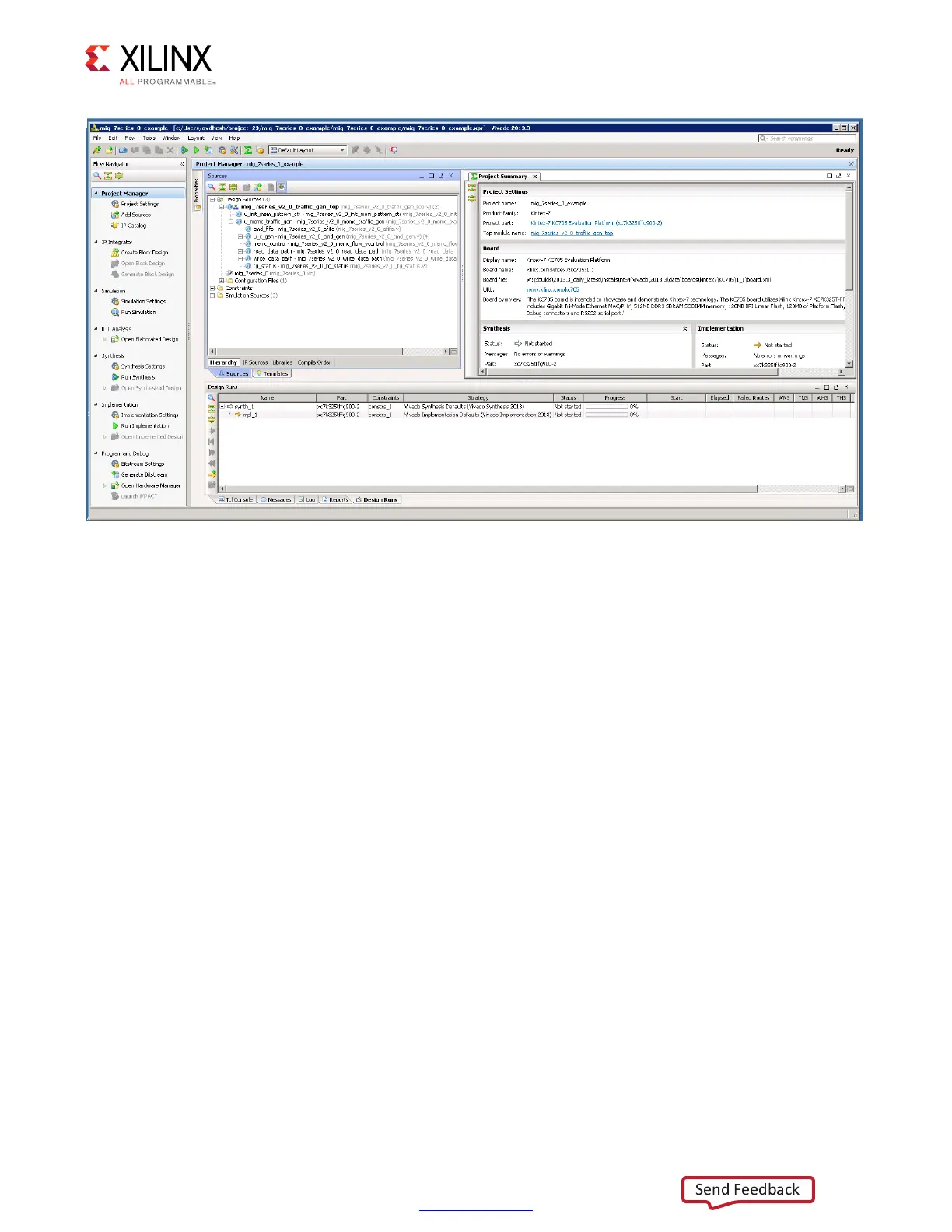

11. Click Generate Bitstream under Project Manager > Program and Debug to generate

the BIT file for the generated design.

The <project directory>/<project directory>.runs/ impl_1 directory

includes all report files generated for the project after running the implementation. It is

also possible to run the simulation in this project.

12. Recustomization of the MIG IP core can be done by using the Recustomize IP option. It

is not recommended to recustomize the IP in the example_design project. The correct

solution is to close the example_design project, go back to original project and

customize there. Right-click the XCI file and click Recustomize IP (Figure 3-34) to open

the MIG GUI and regenerate the design with the preferred options.

X-Ref Target - Figure 3-33

Figure 3-33: Example Design Project

Loading...

Loading...