Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 503

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

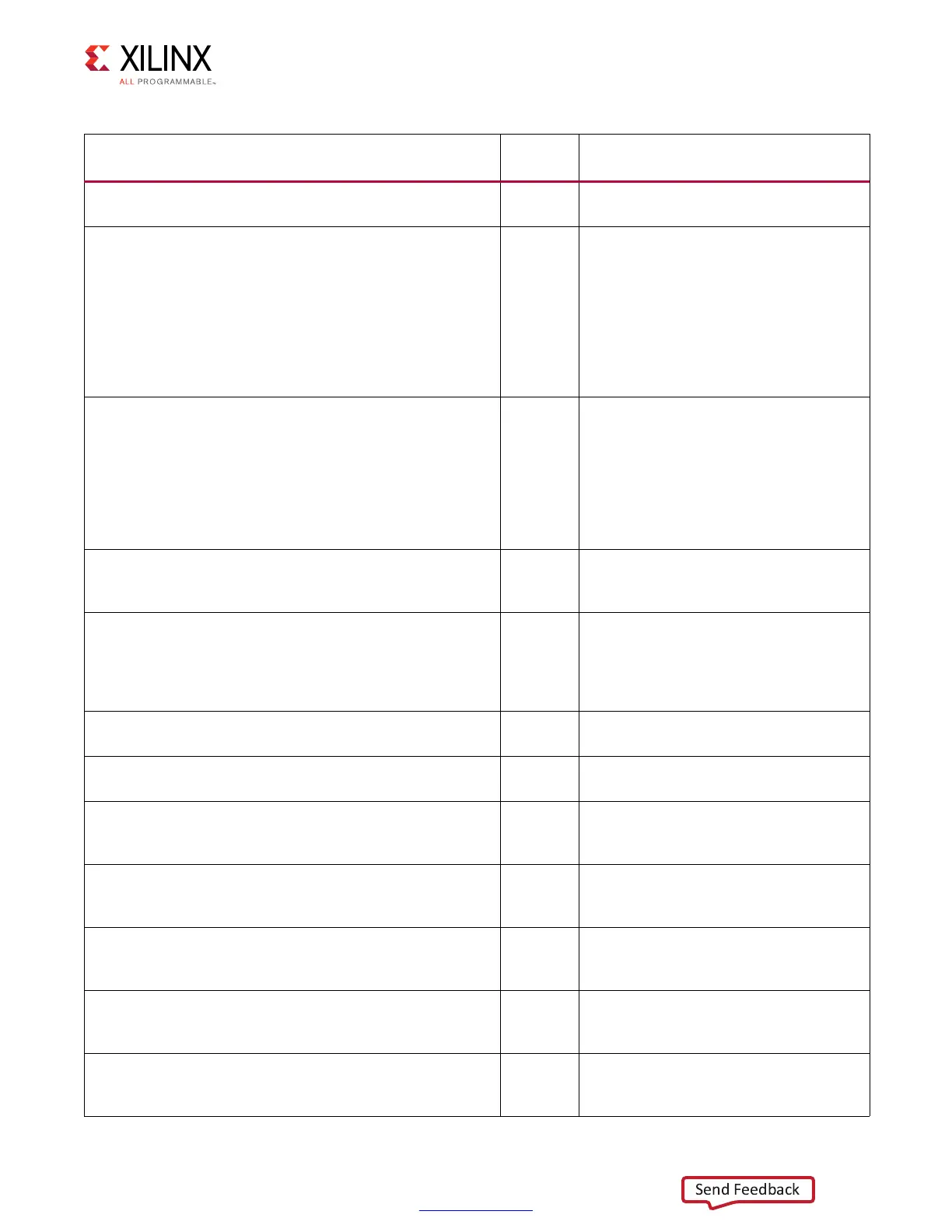

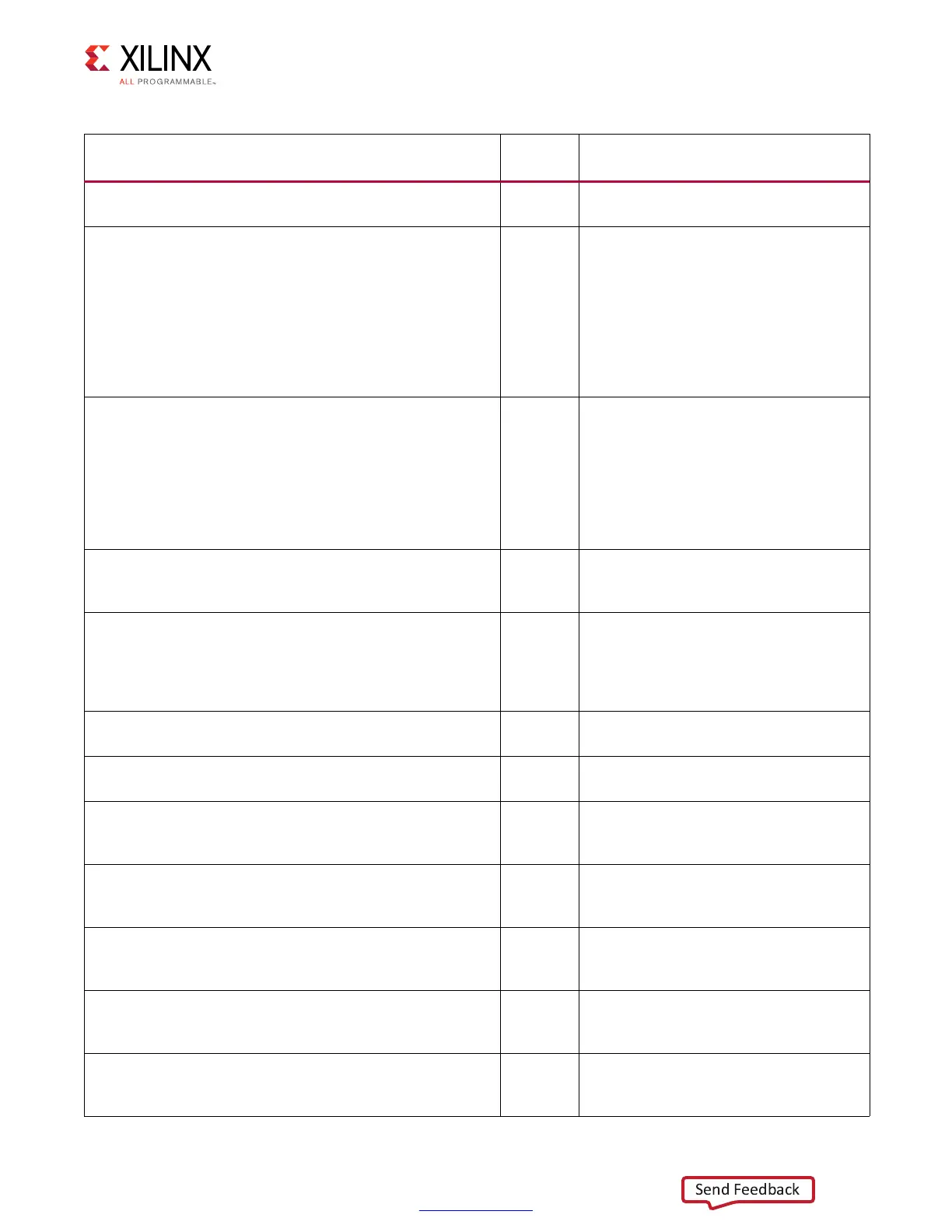

dbg_phy_wr_data[nCK_PER_CLK × 2 × DATA_WIDTH – 1:0] Output

Data being written that is used for debug

with the Vivado logic analyzer feature.

dbg_phy_init_wr_only Input

When this input is High, the state

machine in the rld_phy_write_init_sm

module keeps issuing write commands

for Stage 1 data to the RLDRAM II. This

can be used to verify write timing, for

measuring the DK to DQ timing

relationship at the memory using an

oscilloscope. This signal must be Low for

normal operation.

dbg_phy_init_rd_only Input

When this input is High, the state

machine in the rld_phy_write_init_sm

module keeps issuing read commands

for Stage 1 read calibration. This is useful

to probe the signals on the PCB and look

for any SI issues or verify the previous

write command occurred properly. This

signal must be Low for normal operation.

dbg_byte_sel[CQ_BITS – 1:0] Input

This input selects the corresponding

byte lane and you set the phaser/IDELAY

tap controls.

dbg_bit_sel[Q_BITS – 1:0] Input

This input selects the corresponding bit

lane and you set the IDELAY tap controls.

It also controls which read data signals

are presented to you for debug

(dbg_rd_data_rd and dbg_rd_data_fd).

dbg_idel_up_all Input

This input increments all IDELAY tap

values for the entire bus.

dbg_idel_down_all Input

This input decrements all IDELAY tap

values for the entire bus.

dbg_idel_up Input

This input increments all IDELAY tap

values for a single bit, selected by

dbg_bit_sel.

dbg_idel_down Input

This input decrements all IDELAY tap

values for a single bit, selected by

dbg_bit_sel.

dbg_pi_f_inc Input

This signal increments the PHASER_IN

generated ISERDES clk that is used to

capture rising data.

dbg_pi_f_dec Input

This signal decrements the PHASER_IN

generated ISERDES clk that is used to

capture rising data.

dbg_po_f_inc Input

This signal increments the PHASER_OUT

generated OSERDES clk that is used to

capture falling data.

Table 3-28: DEBUG_PORT Signal Descriptions (Cont’d)

Signal Direction Description

Loading...

Loading...