Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 599

UG586 November 30, 2016

www.xilinx.com

Chapter 4: LPDDR2 SDRAM Memory Interface Solution

The PHY control block has several counters that are not enabled because the synchronous

mode is used where PHY_Clk is 1/2 the frequency of the LPDDR2 SDRAM clock frequency.

At every rising edge of PHY_Clk, a PHY control word is sent to the PHY control block with

information for two memory clock cycles worth of commands and a 2-bit Seq count value.

The write enable to the control FIFO is always asserted and no operation (NOP) commands

are issued between valid commands in the synchronous mode of operation. The Seq count

must be increased with every command sequence of four. The Seq field is used to

synchronize PHY control blocks across multiple I/O banks.

The PHY control block, in conjunction with the PHASER_OUT, generates the write DQS and

the DQ/DQS 3-state control signals during read and write commands.

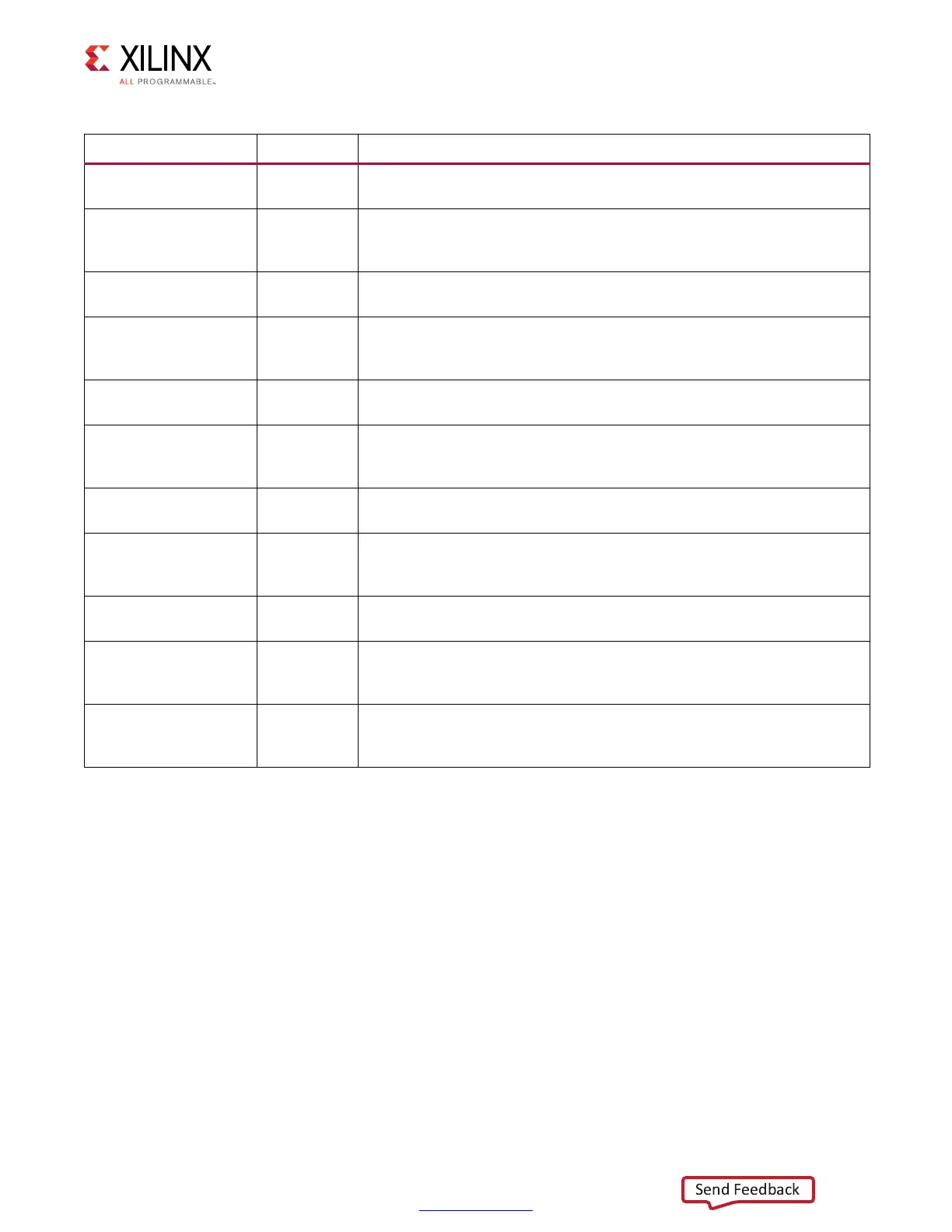

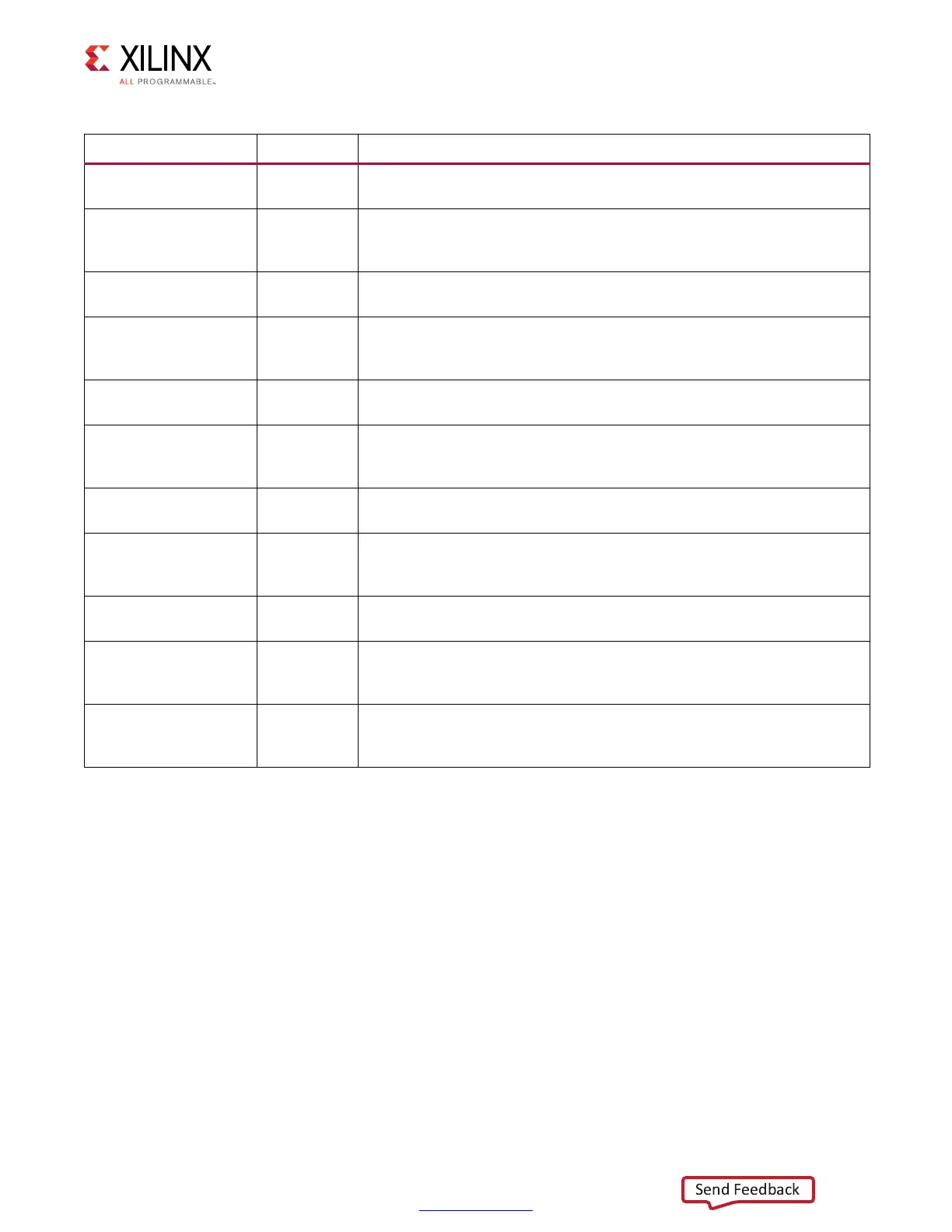

RD_DURATION_1 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles the

auxiliary output remains active for a read command.

WR_CMD_OFFSET_2 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles after the

associated write command is executed that the auxiliary output becomes

active.

WR_DURATION_2 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles the

auxiliary output remains active for a write command.

RD_CMD_OFFSET_2 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles after the

associated read command is executed that the auxiliary output becomes

active.

RD_DURATION_2 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles the

auxiliary output remains active for a read command.

WR_CMD_OFFSET_3 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles after the

associated write command is executed that the auxiliary output becomes

active.

WR_DURATION_3 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles the

auxiliary output remains active for a write command.

RD_CMD_OFFSET_3 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles after the

associated read command is executed that the auxiliary output becomes

active.

RD_DURATION_3 Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles the

auxiliary output remains active for a read command.

CMD_OFFSET Vector[5:0]

This attribute specifies how long in LPDDR2 SDRAM clock cycles after the

associated command is executed that the auxiliary output defined by

AO_TOGGLE toggles.

AO_TOGGLE Vector[3:0]

This attribute specifies which auxiliary outputs are in toggle mode. An

auxiliary output in toggle mode is inverted when its associated AO bit is

set in the PHY control word after the CMD_OFFSET has expired.

Table 4-23: Auxiliary Output Attributes (Cont’d)

Attribute Type Description

Loading...

Loading...