Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 199

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

• The maximum electrical delay between any address and control signals and the

corresponding CK/CK# must be ≤ ±25 ps, with 8 ps being the optimal target.

• CK/CK# signals must arrive at each memory device after the DQS/DQS# signals. The

skew allowed between CK/CK# and DQS/DQS# must be bounded between 0 and

1,600 ps. The recommended skew between CK/CK# and DQS/DQS# is 150 ps to

1,600 ps for components/UDIMMs and for RDIMMs it is 450 ps to 750 ps. For DIMM

modules, the total CK/CK# and DQS/DQS# propagation delays from the FPGA to the

memory components on the DIMM must be accounted for when designing to this

requirement.

• CK/CK# must arrive after DQS/DQS# at each memory component to ensure calibration

can align DQS/DQS# to the correct CK/CK# clock cycle. Write Calibration failures are

seen if this specification is violated. See Debugging Write Calibration Failures

(dbg_wrcal_err = 1), page 253 in the Debugging DDR3/DDR2 Designs, page 228.

The specified DQ to DQS skew limit can be increased if the memory interface is not operated

at the maximum frequency. Table 1-67 indicates the relaxed skew limit (±) for these cases.

The vertical axis is the bit rate in Mb/s. The first column is the FPGA maximum rate, check

the data sheet to determine this maximum rate. The second column is the actual speed the

memory system is operating at. The horizontal axis is the DDR3 SDRAM component speed

rating.

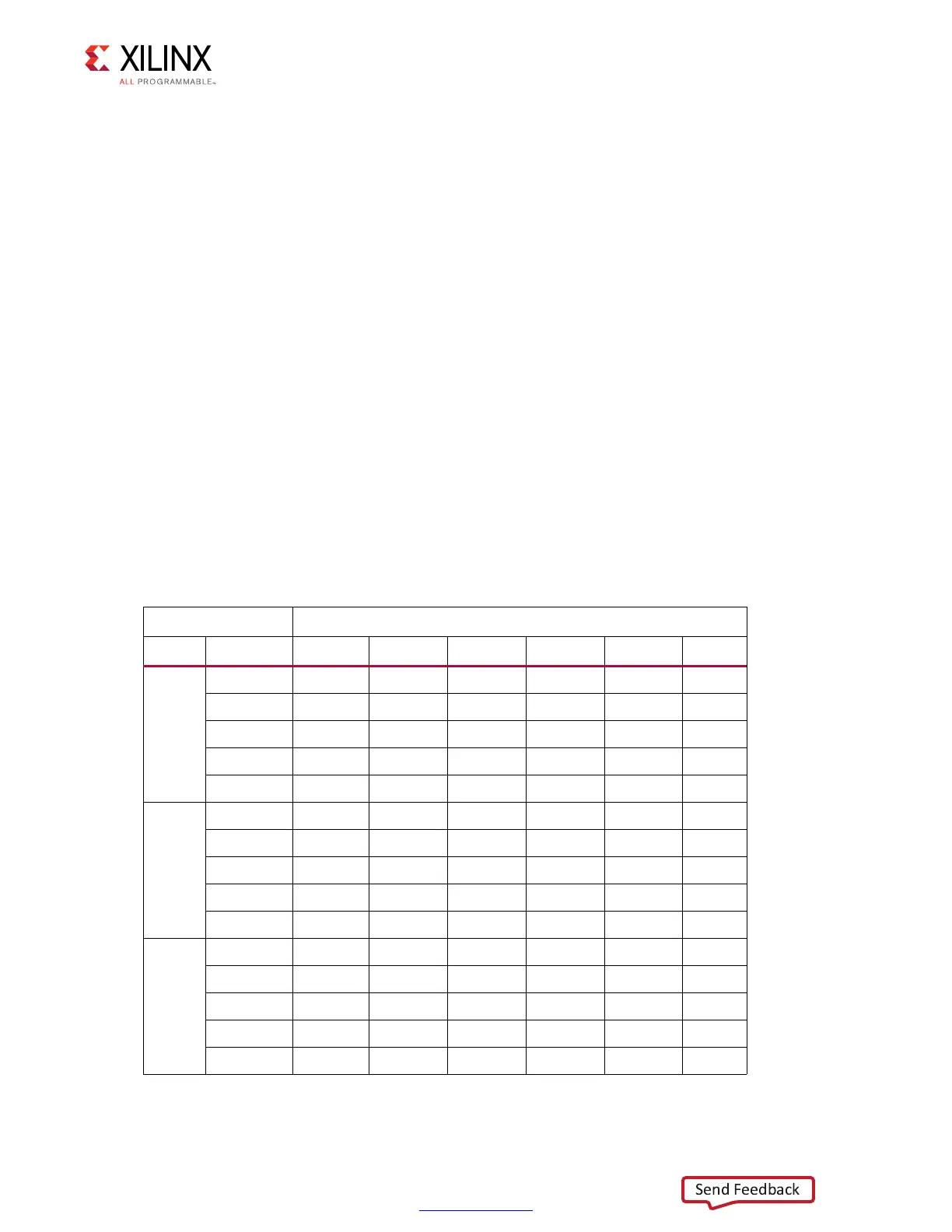

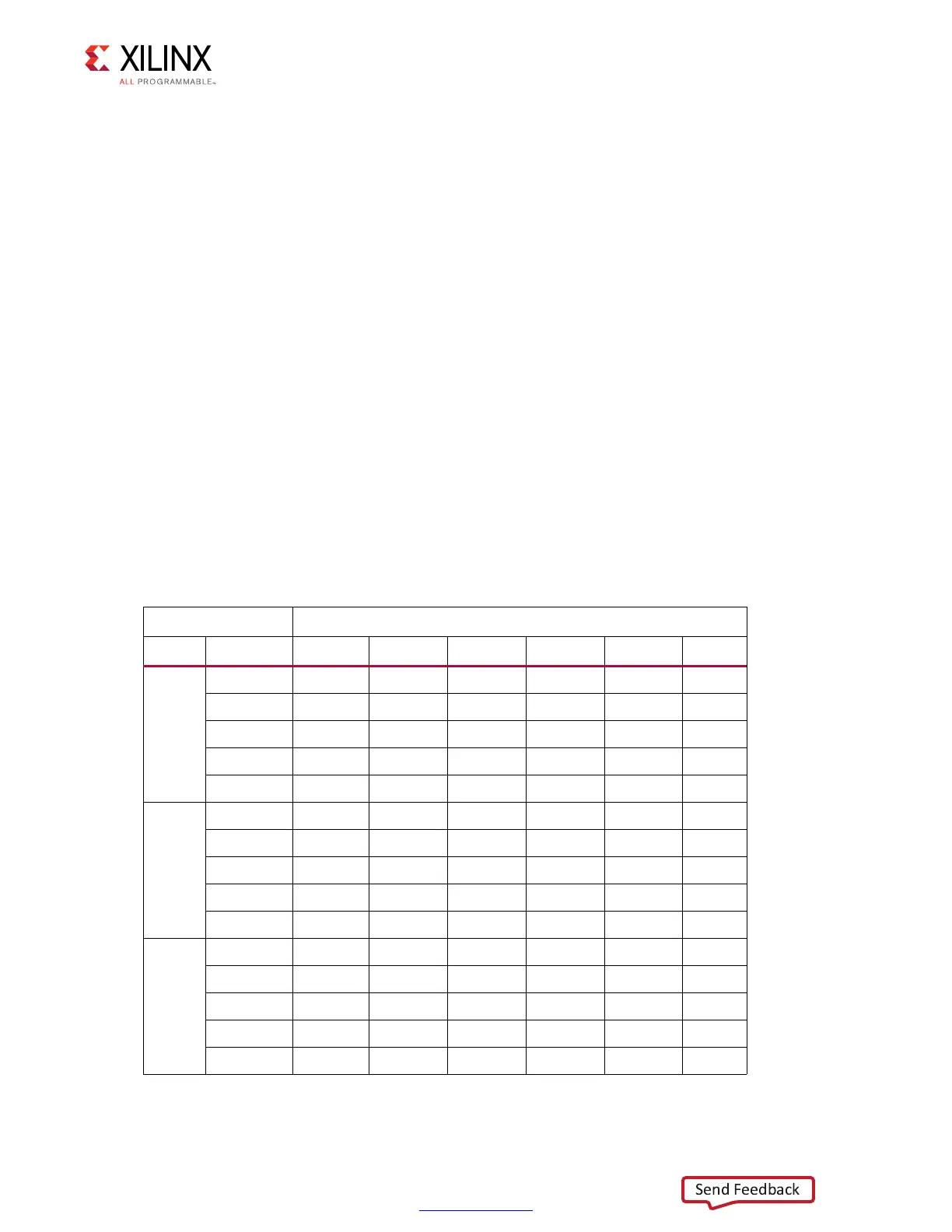

Table 1-67: DQ to DQS Skew Limit

FPGA Rating Memory Component Rating

Rated Actual 2,133 1,866 1,600 1,333 1,066 800

1,866

1,866 18.0 5.0 – – – –

1,600 62.6 49.5 31.3 – – –

1,333 125.2 112.1 93.9 66.4 – –

1,066 150.0 150.0 150.0 150.0 125.4 –

800 150.0 150.0 150.0 150.0 150.0 150.0

1,600

1,866 – – – – – –

1,600 36.2 23.2 5.0 – – –

1,333 98.8 85.8 67.6 40.1 – –

1,066 150.0 150.0 150.0 134.0 99.0 –

800 150.0 150.0 150.0 150.0 150.0 150.0

1,333

1,866 – – – – – –

1,600 – – – – – –

1,333 63.7 50.7 32.5 5.0 – –

1,066 150.0 144.7 126.4 98.9 63.9 –

800 150.0 150.0 150.0 150.0 150.0 150.0

Loading...

Loading...