Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 457

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

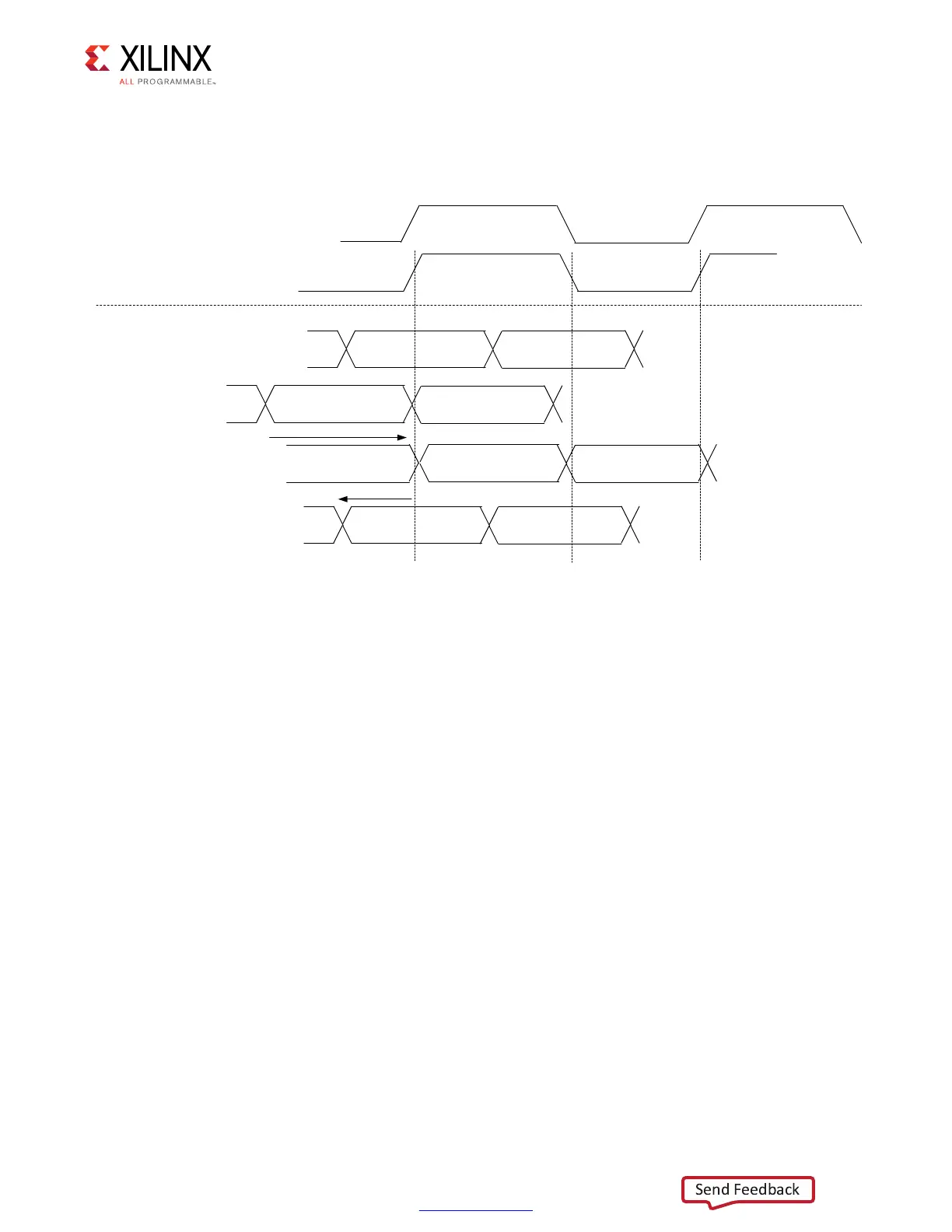

Figure 3-59 shows the steps taken for a byte lane for RLDRAM 3. The data is adjusted with

respect to the DK clock coming from another bank. This is the same as RLDRAM 3 stage 3,

just the first two stages of calibration are skipped for RLDRAM 3.

When write calibration completes, the read calibration is restarted one last time to run with

the proper write settings and allowed to complete through read valid generation.

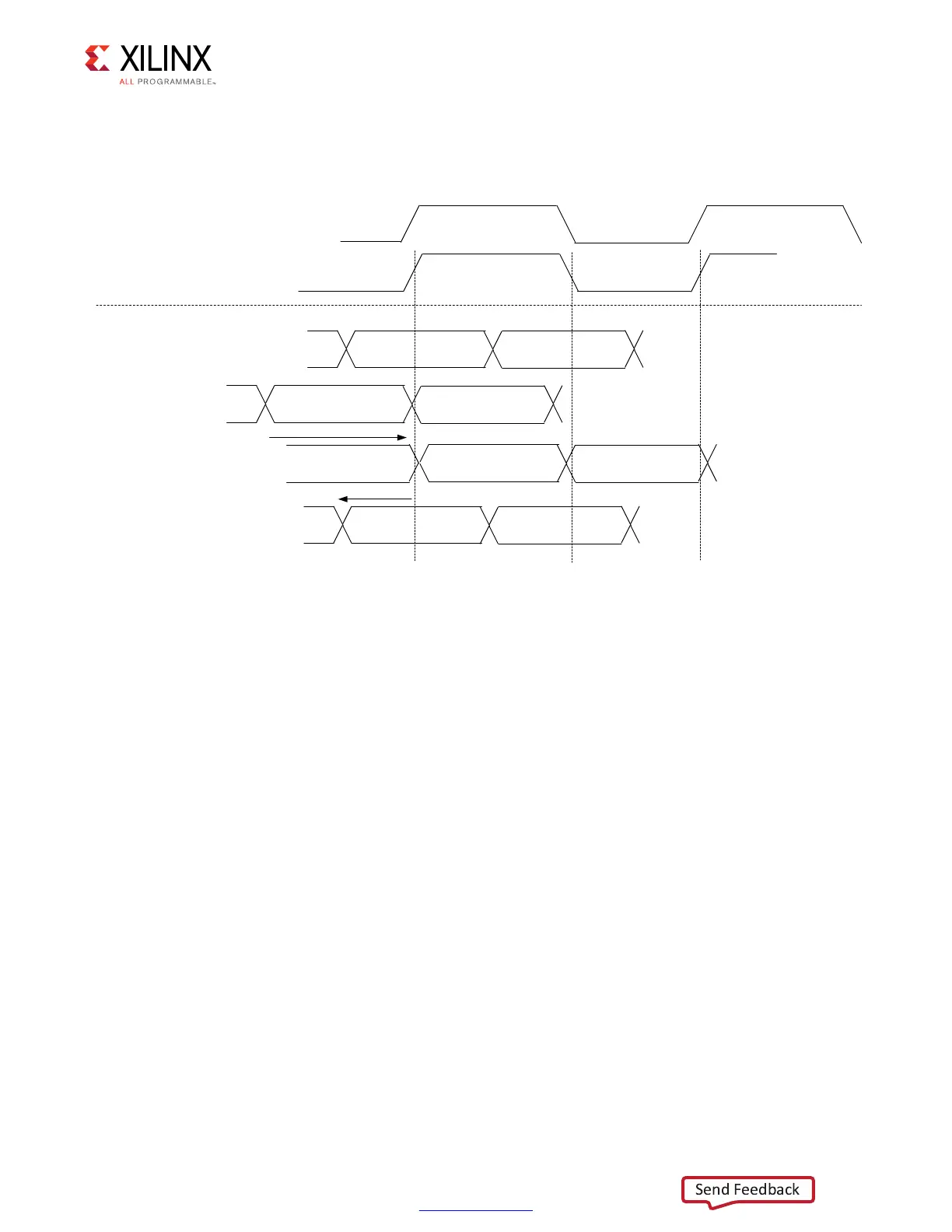

The simulation waveforms for write calibration of a 36-bit RLDRAM II design is shown in

Figure 3-60. The state machine steps through the calibration one byte at a time, selecting

the PHASERs for a given byte lane, making adjustments, and recording the results to

optimize the write timing. Adjustments are only made within the limits of the PHASER_OUT

fine tap delay. To debug any problems, it is important to check the margin found during

both read and write calibration, and to check the cmd-to-data write latency seen by the

DRAM matches what is programmed in the MRS register. For more details, see Debugging

RLDRAM II and RLDRAM 3 Designs, page 481.

X-Ref Target - Figure 3-59

Figure 3-59: RLDRAM 3 Write Calibration (Stage 3, DK-to-DQ2)

Byte lane

without a

DK

Rise

DQ

Fall

Rise

DQ

Fall

Starting

point, 32

taps

Rise

DQ

Fall

Start the

sweep at

0 taps

Sweep until window

edge found or end

of taps

(1)

(2)

(3)

Rise

DQ

Fall

Final

Setting

(4)

Data Shift

Data Shift

Fall

A/C Bank

CK

DK

Loading...

Loading...